聯(lián)系我們

Contact Us公司總機(jī):020-8998-6280

技術(shù)熱線:020-3893-9734

技術(shù)郵箱:support@tronlong.com

銷售郵箱:sales@tronlong.com

FPGA的HLS案例開發(fā)|基于Kintex-7、Zynq-7045_7100開發(fā)板

2021/02/19

FPGA的HLS案例開發(fā)|基于Kintex-7、Zynq-7045_7100開發(fā)板

前 言

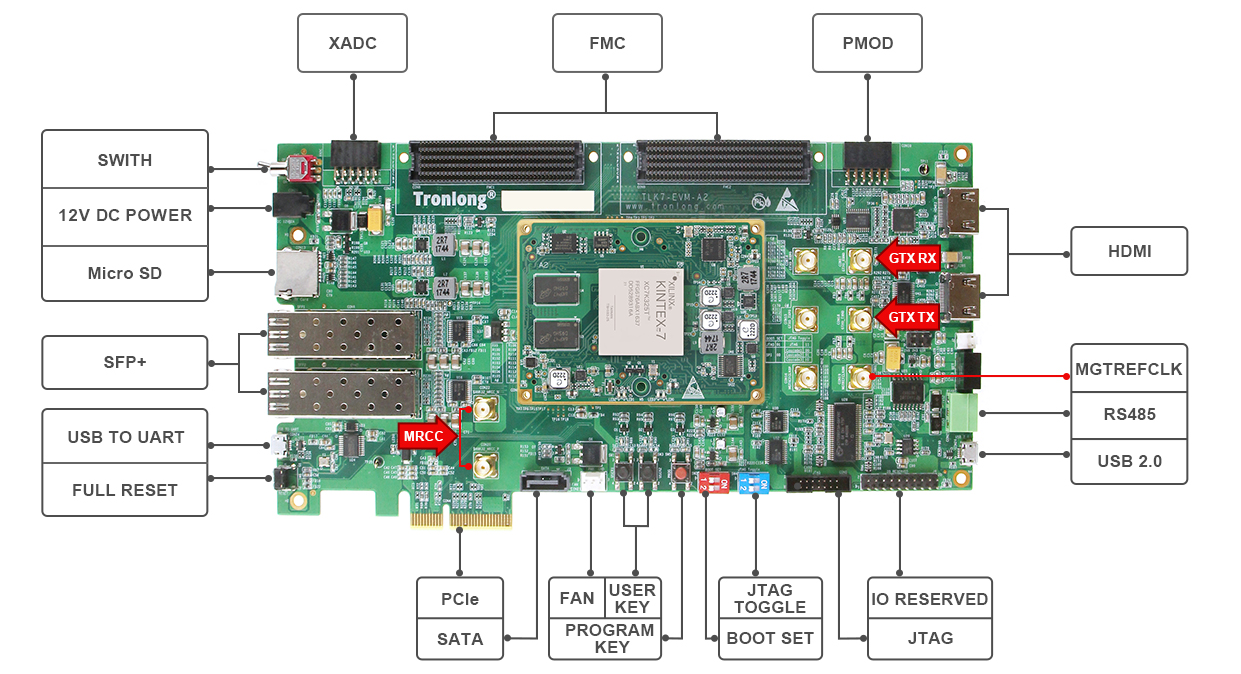

本文基于創(chuàng)龍科技TLK7-EVM開發(fā)板,是一款基于Xilinx Kintex-7系列FPGA設(shè)計(jì)的高端評(píng)估板,由核心板和評(píng)估底板組成。核心板經(jīng)過專業(yè)的PCB Layout和高低溫測試驗(yàn)證,穩(wěn)定可靠,可滿足各種工業(yè)應(yīng)用環(huán)境。

評(píng)估板接口資源豐富,引出FMC、SFP+、PCIe、SATA、HDMI等接口,方便用戶快速進(jìn)行產(chǎn)品方案評(píng)估與技術(shù)預(yù)研。

圖1 TLK7-EVM評(píng)估板

開發(fā)案例主要包括:

l CameraLink、SDI、HDMI、PAL視頻輸入/輸出案例

l 高速AD(AD9613)采集+高速DA(AD9706)輸出案例

l AD9361軟件無線電案例

l UDP(10G)光口通信案例

l UDP(1G)光口通信案例

l Aurora光口通信案例

l PCIe通信案例

l 案例源碼、產(chǎn)品資料(用戶手冊(cè)、核心板硬件資料、產(chǎn)品規(guī)格書):site.tronlong.com/pfdownload

本文主要介紹HLS案例的使用說明,適用開發(fā)環(huán)境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx VivadoHLS 2017.4、Xilinx SDK 2017.4。

Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持將C、C++等語言轉(zhuǎn)化成硬件描述語言,同時(shí)支持基于OpenCL等框架對(duì)Xilinx可編程邏輯器件進(jìn)行開發(fā),可加速算法開發(fā)的進(jìn)程,縮短產(chǎn)品上市時(shí)間。

HLS基本開發(fā)流程如下:

(1) HLS工程新建/工程導(dǎo)入

(2) 編譯與仿真

(3) 綜合

(4) IP核封裝

(5) IP核測試

HLS案例位于產(chǎn)品資料“4-軟件資料\Demo\FPGA-HLS-demos\”目錄下,案例目錄詳細(xì)說明如下表。

表1

|

hls_ip_demo |

bin |

IP核測試程序可執(zhí)行文件 |

|

|

project |

IP核測試程序Vivado工程 |

||

|

vivado_hls |

ip_package |

IP核 |

|

|

poject |

solution1 |

仿真方案 |

|

|

src |

HLS工程源碼 |

||

|

test_bench |

HLS工程仿真程序或測試文件 |

||

|

vivado_hls.app |

HLS工程文件 |

||

HLS詳細(xì)開發(fā)說明可參考產(chǎn)品資料“6-開發(fā)參考資料\Xilinx官方參考文檔\”目錄下的《ug871-vivado-high-level-synthesis-tutorial.pdf》和《ug902-vivado-high-level-synthesis.pdf》。

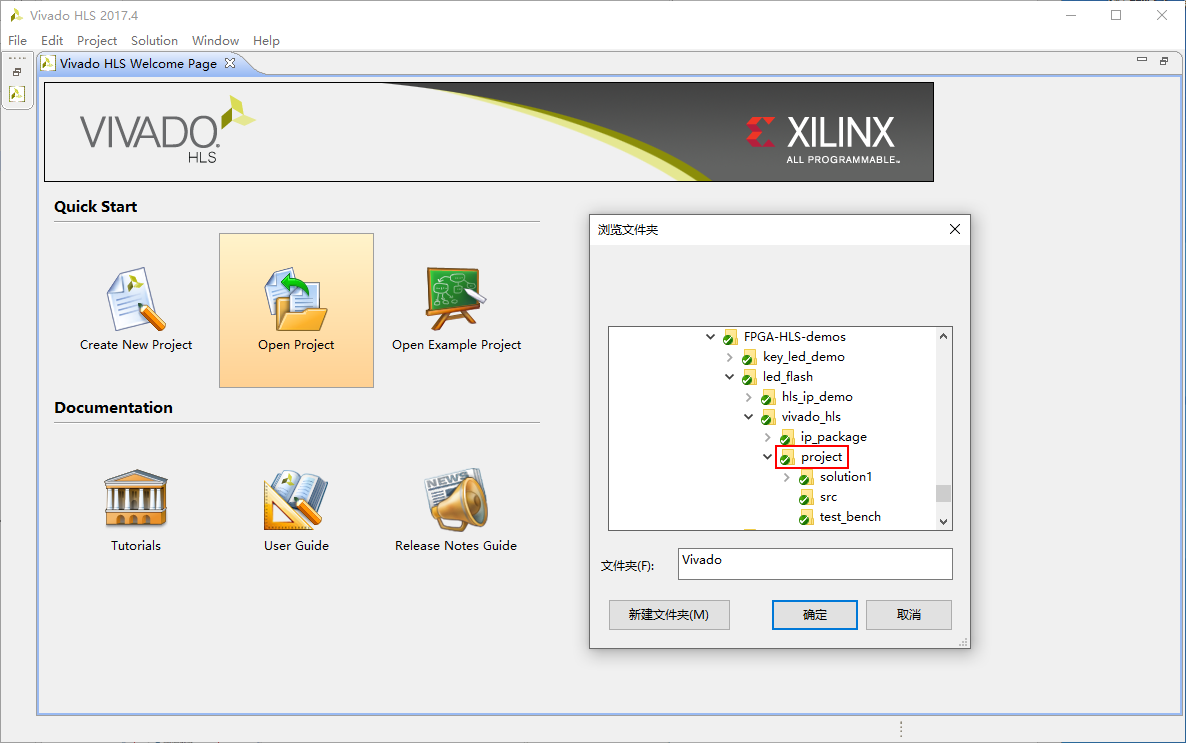

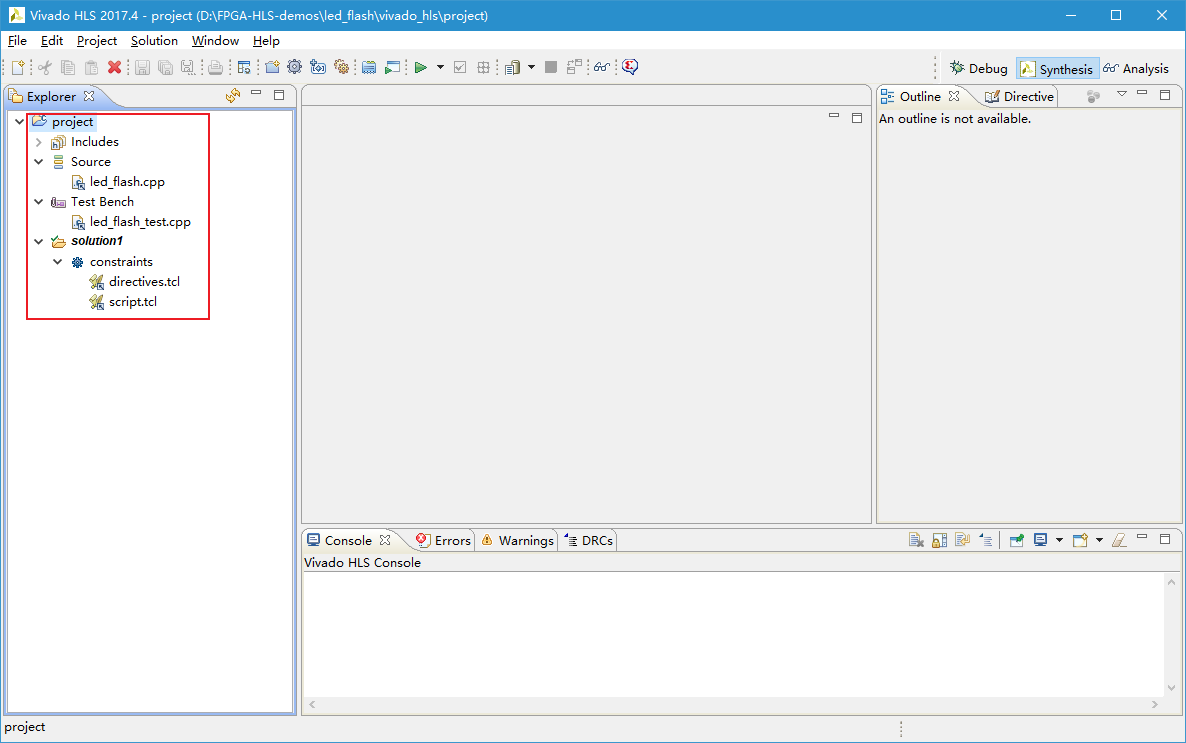

HLS工程導(dǎo)入

雙擊桌面如下圖標(biāo)打開Xilinx Vivado HLS 2017.4,并在彈出的界面中點(diǎn)擊“Open Project”選擇案例“vivado_hls\project\”目錄,然后點(diǎn)擊“確定”導(dǎo)入HLS工程。

圖2

圖3

圖4

亦可新建HLS工程,并使用C/C++等語言進(jìn)行程序編寫。

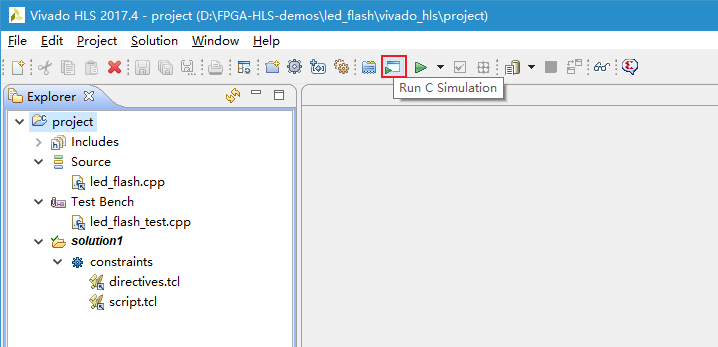

編譯和仿真C代碼

仿真程序位于工程的test_bench目錄下,用于驗(yàn)證src目錄下的HLS工程源碼。

導(dǎo)入HLS工程后,點(diǎn)擊![]() (Run C Simulation)進(jìn)行編譯與仿真。

(Run C Simulation)進(jìn)行編譯與仿真。

圖5

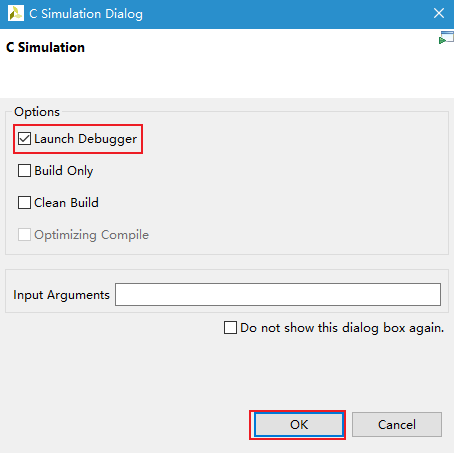

彈出如下界面,勾選“Launch Debugger”,并點(diǎn)擊OK。

圖6

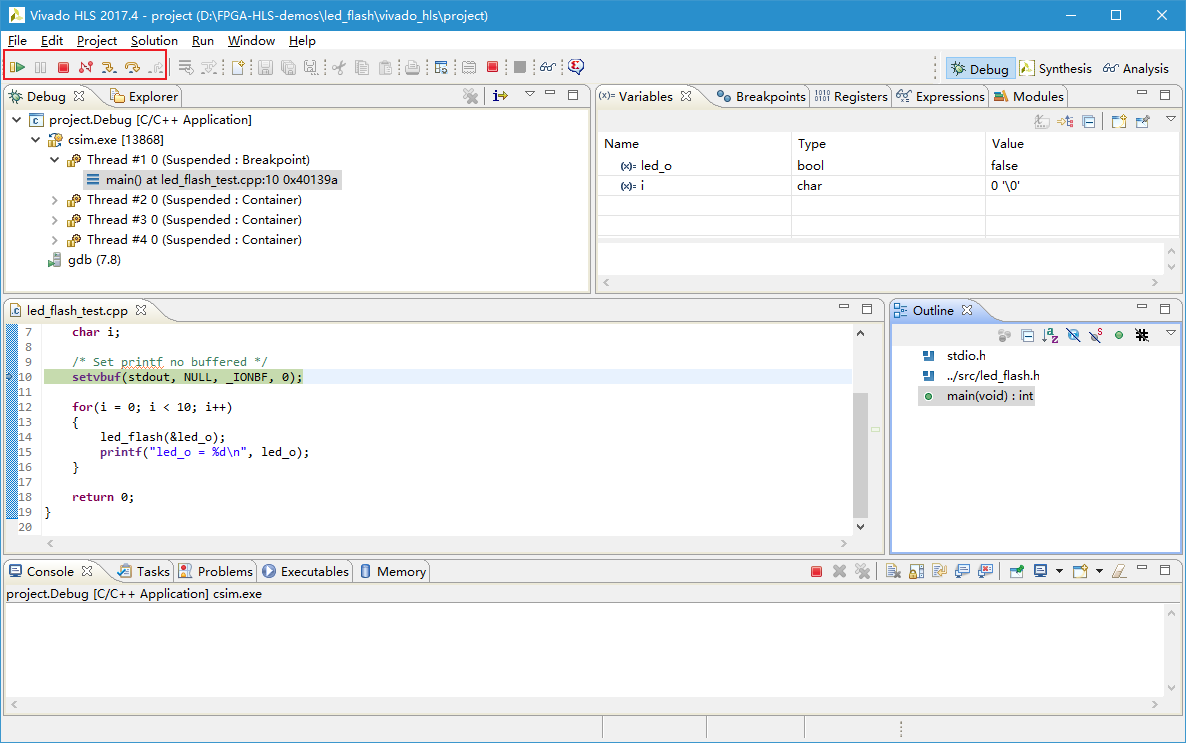

編譯完成后即可全速或單步運(yùn)行仿真代碼。

圖7

綜合

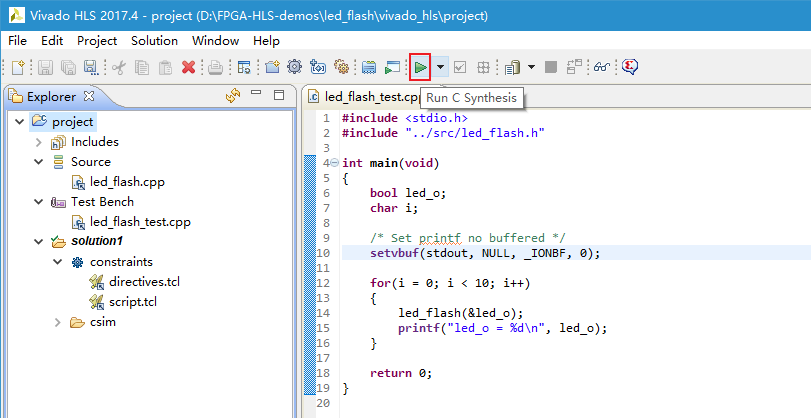

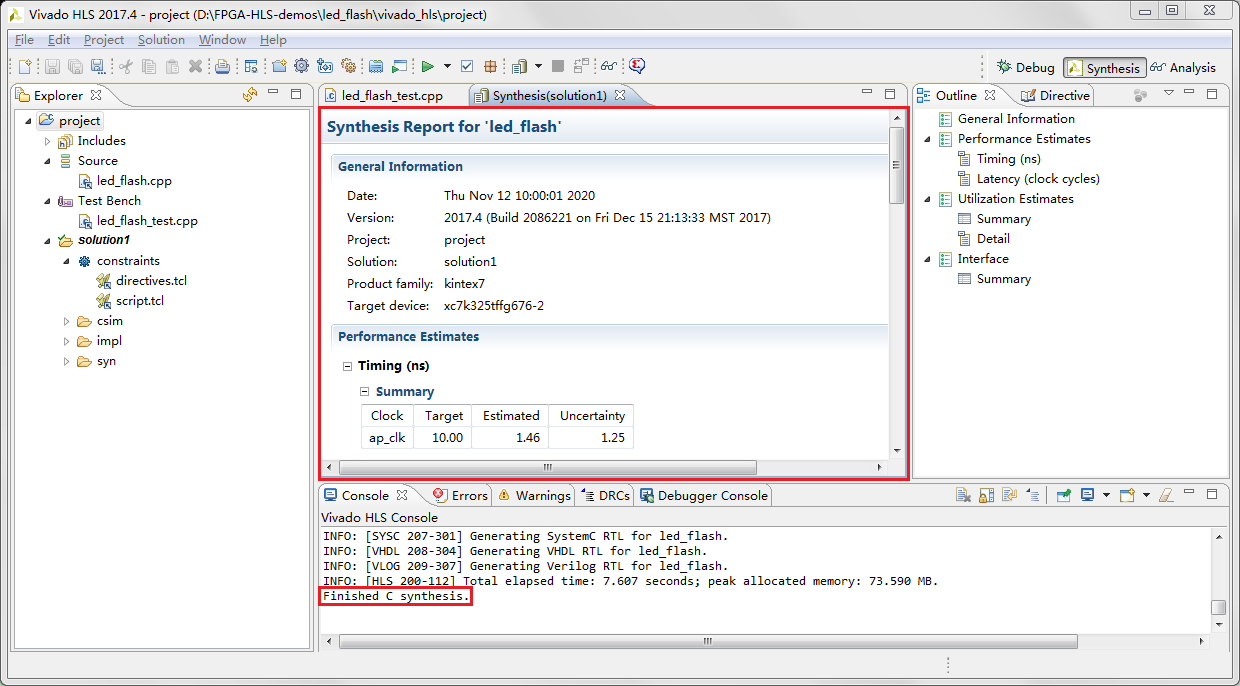

本小節(jié)演示將C/C++等程序綜合成為RTL設(shè)計(jì),并生成綜合報(bào)告。

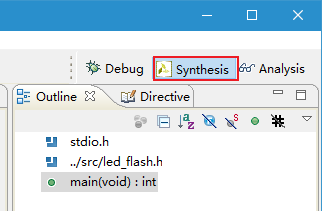

點(diǎn)擊界面右上角Synthesis返回至工程界面,然后點(diǎn)擊![]() 進(jìn)行綜合。

進(jìn)行綜合。

圖8

圖9

綜合完成后,報(bào)表文件將自動(dòng)打開。

圖10

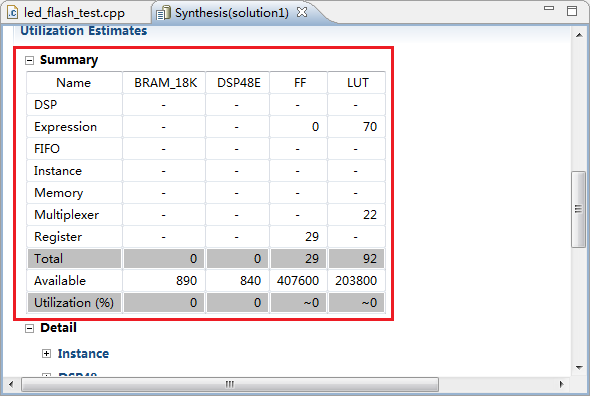

通過報(bào)表文件可查看本設(shè)計(jì)的時(shí)延、資源占用等信息。

圖11

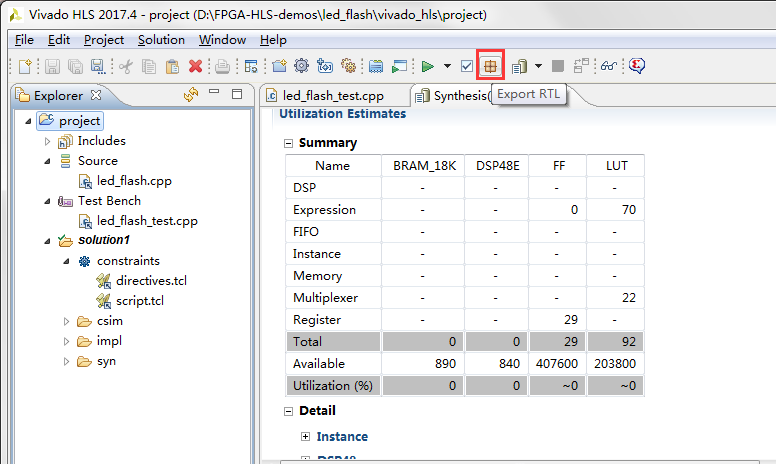

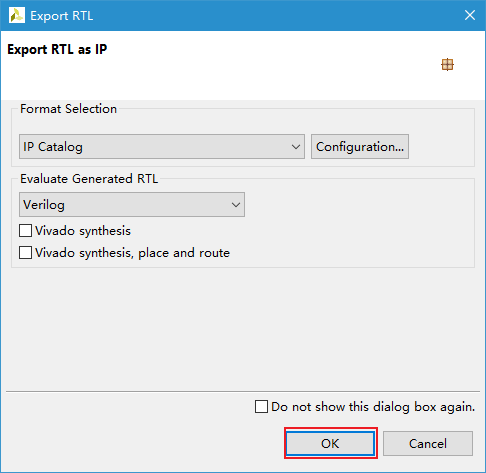

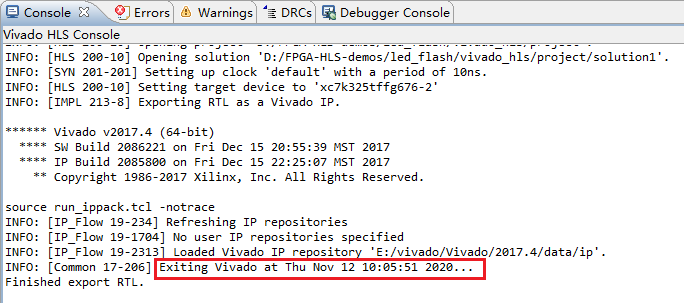

IP核封裝

綜合完成后,點(diǎn)擊![]() 生成IP核。

生成IP核。

圖12

圖13

圖14

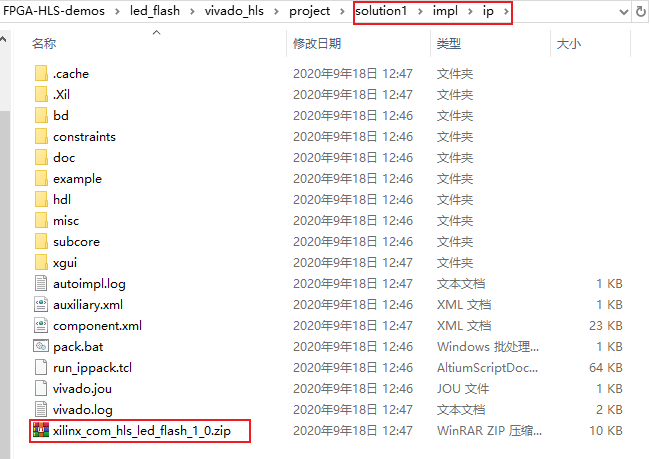

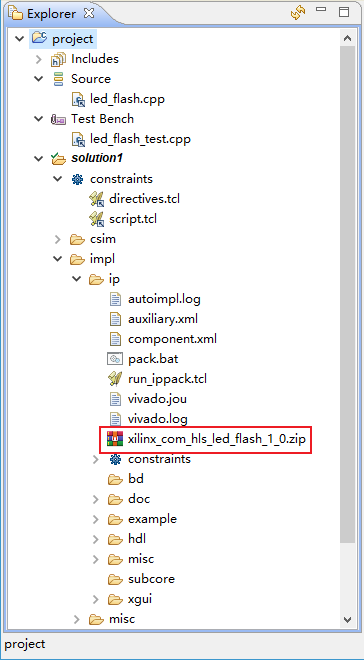

運(yùn)行完成后,將會(huì)在案例“vivado_hls\project\solution1\impl\ip\”目錄下生成IP核。

圖15

圖16

IP核測試

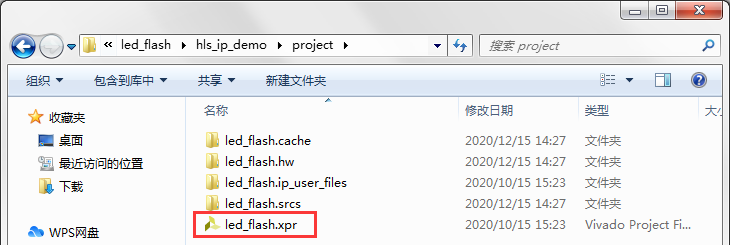

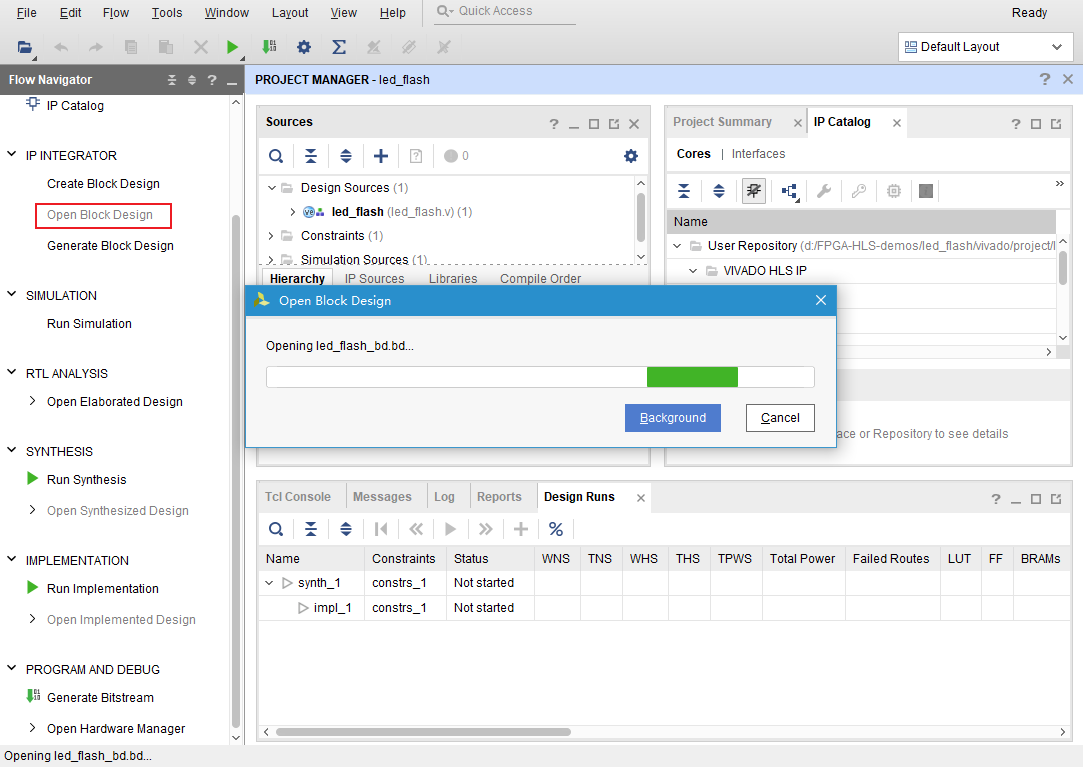

進(jìn)入案例“hls_ip_demo\project\”的IP核測試程序Vivado工程目錄,雙擊.xpr文件打開工程,工程默認(rèn)已添加待測試的IP核。

圖17

如需自行導(dǎo)入IP核,請(qǐng)參考如下步驟。

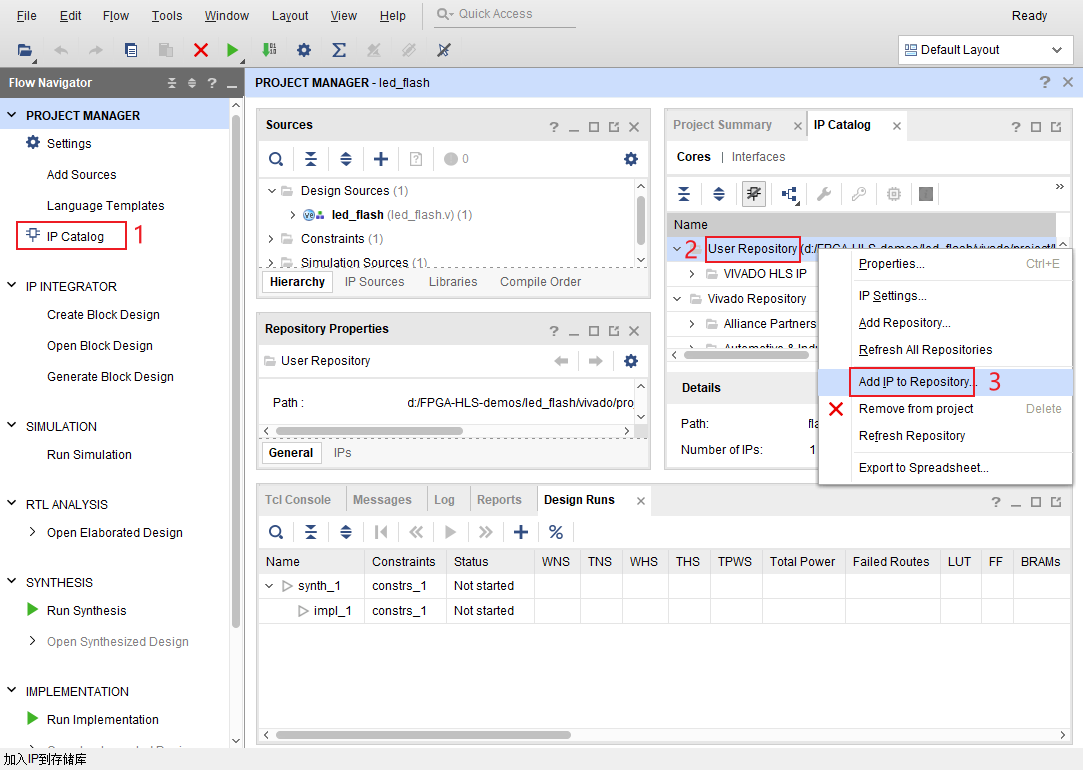

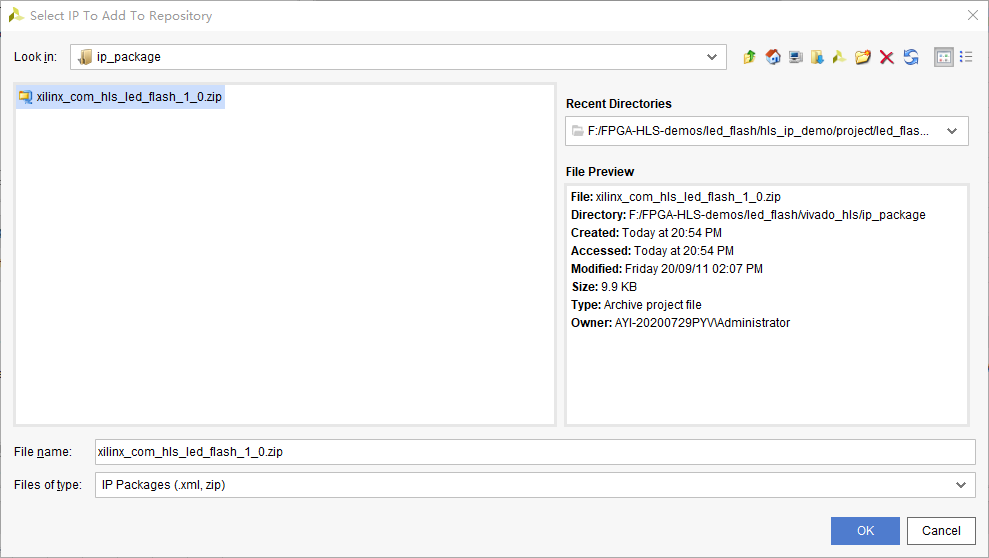

(1) 請(qǐng)點(diǎn)擊“IP Catalog -> User Repository -> Add IP to Repository…”,在彈出的界面中選擇IP核后點(diǎn)擊OK。

圖18

圖19

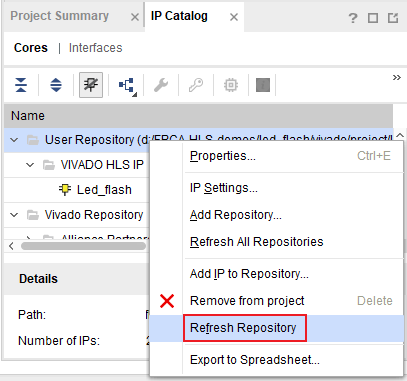

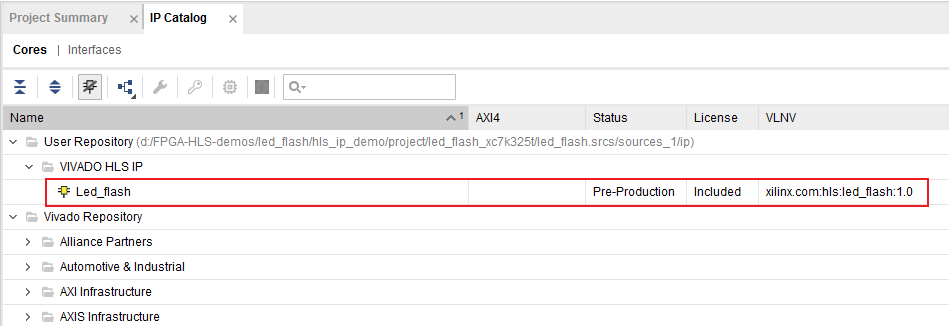

(2) 右擊“User Repository”后點(diǎn)擊“Refresh Repository”,即可看到添加的IP核。

圖20

圖21

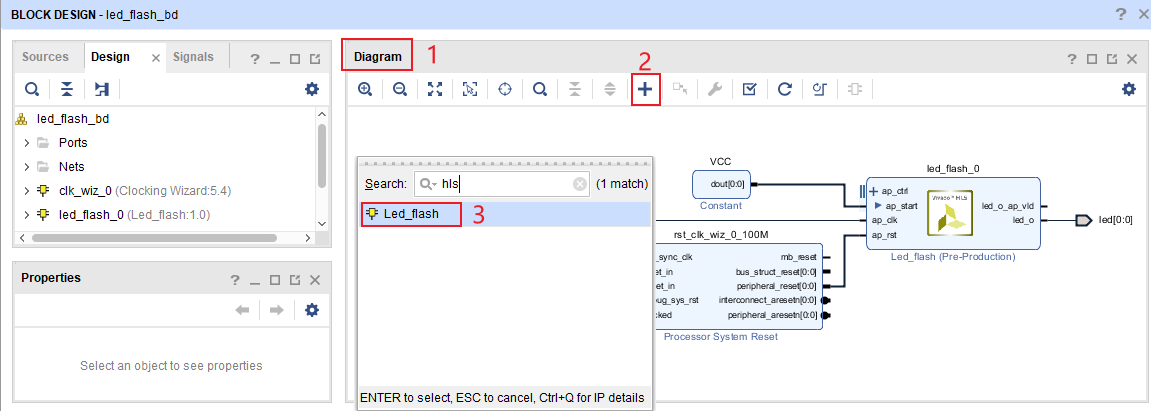

(3) 如需添加Vivado自帶的IP核,點(diǎn)擊“Open Block Design”,在彈出的界面中點(diǎn)擊![]() ,并選擇所需IP核將其導(dǎo)入工程。

,并選擇所需IP核將其導(dǎo)入工程。

圖22

圖23

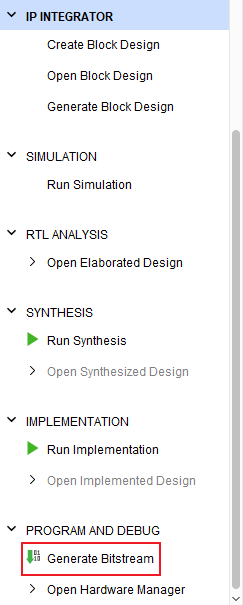

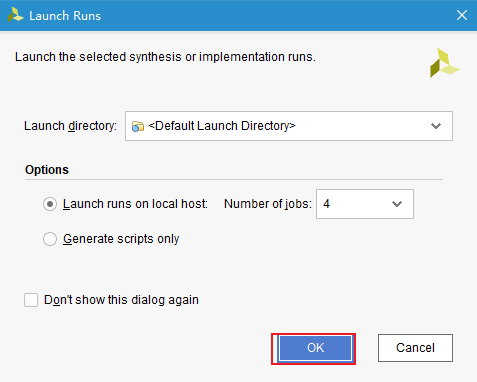

點(diǎn)擊Vivado界面左側(cè)的“Generate Bitstream”選項(xiàng),在彈出的界面中點(diǎn)擊OK進(jìn)行IP核測試程序Vivado工程編譯。

圖24

圖25

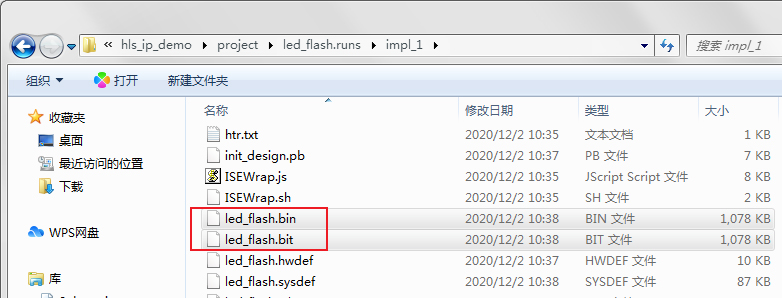

編譯完成后,將會(huì)在工程“l(fā)ed_flash.runs\impl_1\”目錄下生成.bit和.bin格式可執(zhí)行文件。

圖26

請(qǐng)參考基于Vivado的FPGA程序加載與固化手冊(cè)加載.bit格式可執(zhí)行文件,即可看到評(píng)估底板的LED2進(jìn)行閃爍。

l 更多推薦

圖27

服務(wù)熱線

服務(wù)熱線