聯(lián)系我們

Contact Us公司總機(jī):020-8998-6280

技術(shù)熱線:020-3893-9734

技術(shù)郵箱:support@tronlong.com

銷售郵箱:sales@tronlong.com

基于FPGA的兩種SDI視頻方案(GTX+外接芯片)

2021/02/04

前言

SDI接口,全稱是“數(shù)字分量串行接口(Serial Digital Interface)”。按速率可分為標(biāo)準(zhǔn)清新度SD-SDI、高清標(biāo)準(zhǔn)HD-SDI和3G-SDI,其對(duì)應(yīng)速率分別是270Mb/s、1.485Gb/s和2.97Gb/s。目前在航空航天、軍事、醫(yī)療、交通等領(lǐng)域,SDI的應(yīng)用廣泛度僅次于CameraLink接口。

圖1

SDI接口優(yōu)勢(shì):

(1) 消耗GTX更少,消耗IO更少

如果使用GTX總線,僅需1對(duì)GTX,而HDMI則需要3對(duì)GTX。CameraLink接口由于走LVDS信號(hào),Base模式下需要11對(duì)LVDS信號(hào),F(xiàn)ull模式下需要22對(duì)LVDS信號(hào),消耗IO數(shù)量比GTX SDI多了很多。

(2) 傳輸更穩(wěn)定

相較于HDMI接口,SDI接口的自鎖扣設(shè)計(jì)更加穩(wěn)定可靠,不易脫落,不會(huì)因人為因素造成信號(hào)中斷。

(3) 傳輸距離更長(zhǎng)

串行接口是指逐位數(shù)據(jù)的順序傳輸。它的特點(diǎn)是通訊線簡(jiǎn)單。只要一對(duì)傳輸線可以實(shí)現(xiàn)雙向通信,特別適合于長(zhǎng)距離通信。從理論上講,SDI的傳輸距離可以達(dá)到100m。

(4) 成本更低

SDI接口平均每米價(jià)格約為4元,相較于HDMI接口的平均每米價(jià)格約為10元,SDI接口成本更低。

創(chuàng)龍科技(Tronlong)的Kintex-7、Zynq-7045/7100等FPGA板卡通過FMC視頻模塊已實(shí)現(xiàn)兩種SDI視頻輸入/視頻輸出方案:GTX +外接芯片。本文將為您分享基于Kintex-7 FPGA評(píng)估板、TL2971A/2972F視頻模塊的3G-SDI視頻輸入/輸出開發(fā)案例,使用外接芯片方式。TL2971A/2972F視頻模塊模塊亦可支持GTX方式。

1 硬件平臺(tái)

本文基于創(chuàng)龍科技TLK7-EVM評(píng)估板、TL2971A/2972F視頻模塊進(jìn)行演示。

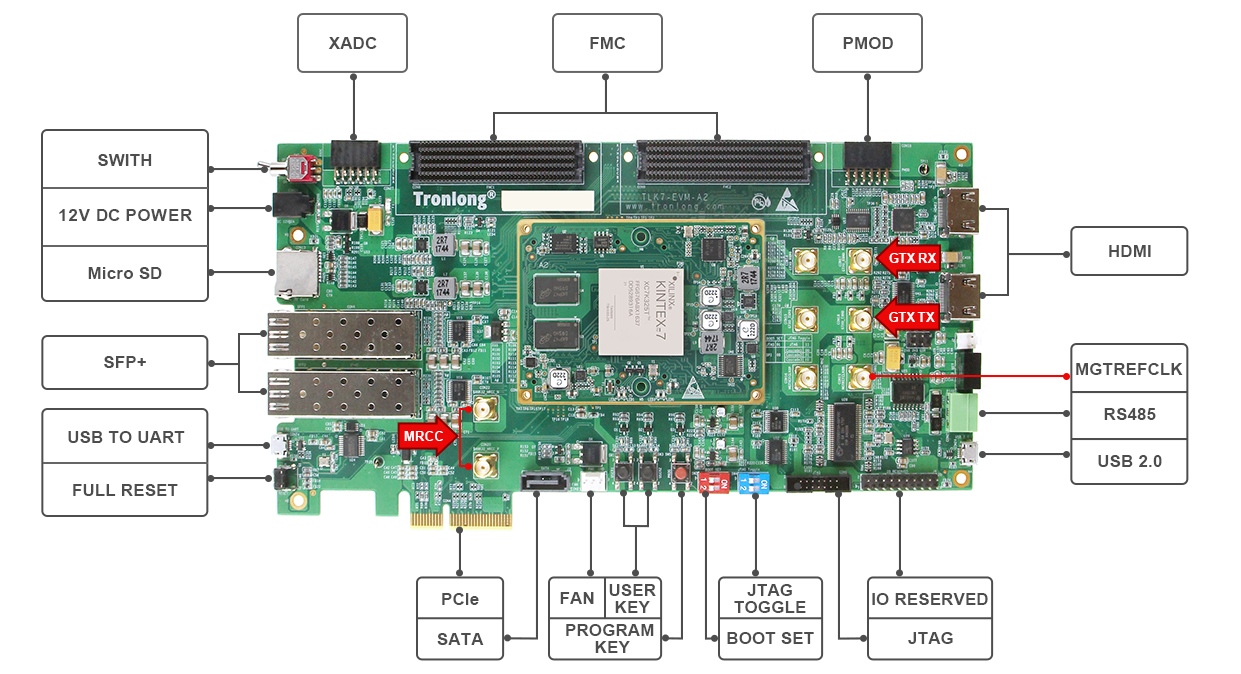

1.1 TLK7-EVM評(píng)估板

TLK7-EVM是一款基于Xilinx Kintex-7系列FPGA設(shè)計(jì)的高端評(píng)估板,由核心板和評(píng)估底板組成。核心板經(jīng)過專業(yè)的PCB Layout和高低溫測(cè)試驗(yàn)證,穩(wěn)定可靠,可滿足各種工業(yè)應(yīng)用環(huán)境。

評(píng)估板接口資源豐富,引出FMC、SFP+、PCIe、SATA、HDMI等接口,方便用戶快速進(jìn)行產(chǎn)品方案評(píng)估與技術(shù)預(yù)研。

圖2 TLK7-EVM評(píng)估板

開發(fā)案例主要包括:

l CameraLink、SDI、HDMI、PAL視頻輸入/輸出案例

l 高速AD(AD9613)采集+高速DA(AD9706)輸出案例

l AD9361軟件無線電案例

l UDP(10G)光口通信案例

l UDP(1G)光口通信案例

l Aurora光口通信案例

l PCIe通信案例

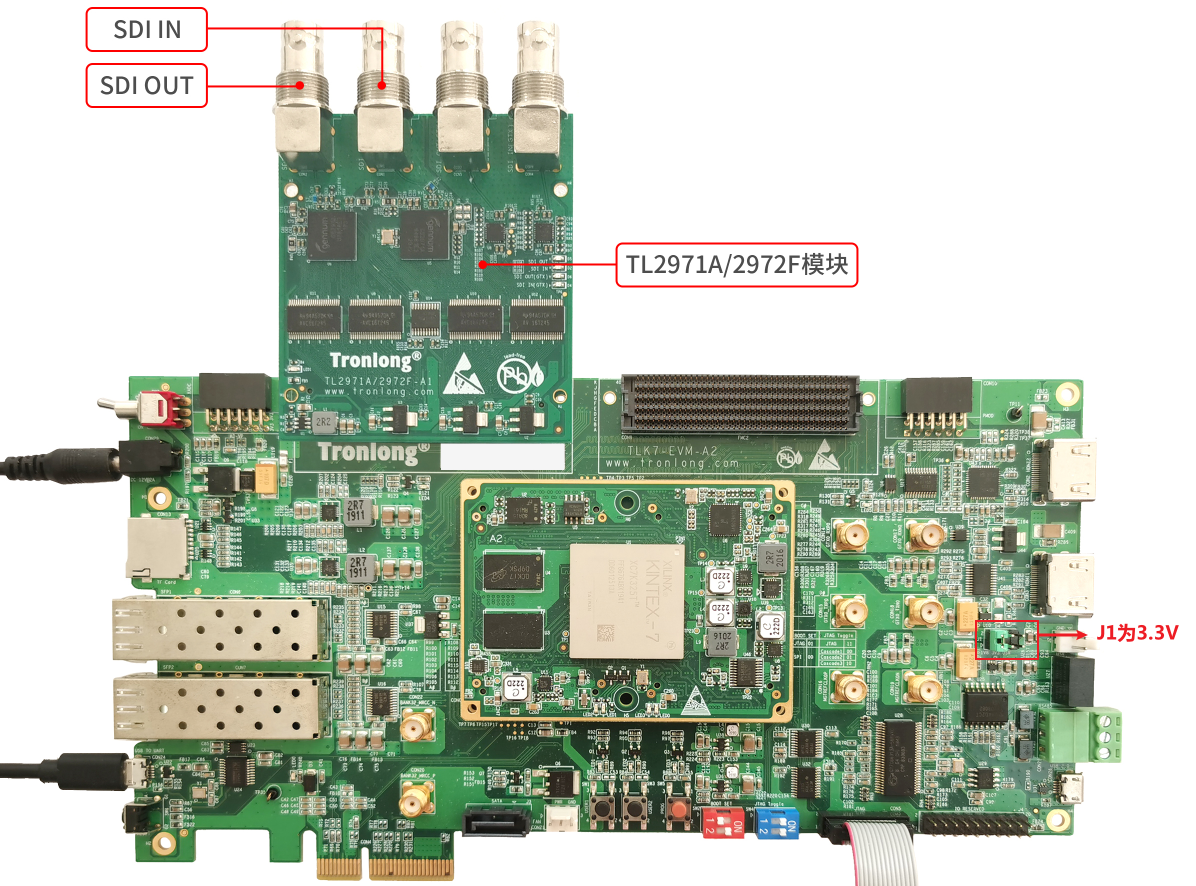

1.2 TL2971A/2972F視頻模塊

TL2971A/2972F是一款基于FMC LPC標(biāo)準(zhǔn)設(shè)計(jì)的3G-SDI視頻輸入/輸出模塊,與創(chuàng)龍科技Zynq-7000/Kintex-7/Artix-7等評(píng)估板配套使用。以下為此模塊特點(diǎn):

(1)通過GTX高速串行總線引出1路SDI視頻輸入接口,最高支持2.97Gb/s(1080P60)。

(2)通過GTX高速串行總線引出1路SDI視頻輸出接口,最高支持2.97Gb/s(1080P60)。

(3)通過GS2971A芯片引出1路SDI視頻輸入接口,最高支持2.97Gb/s(1080P60)。

(4)通過GS2972芯片引出1路SDI視頻輸出接口,最高支持2.97Gb/s(1080P60)。

(5)采用標(biāo)準(zhǔn)BNC連接器,支持視頻設(shè)備熱插拔。

圖3 TL2971A/2972F視頻模塊

案例源碼、產(chǎn)品資料(用戶手冊(cè)、核心板硬件資料、產(chǎn)品規(guī)格書)可點(diǎn)擊下方鏈接或掃碼二維碼獲取。

http://site.tronlong.com/pfdownload

圖4

掃描下方二維碼,即可申請(qǐng)TLK7-EVM評(píng)估板進(jìn)行快速評(píng)估,免費(fèi)哦!

圖5

2 案例功能

本案例為通過GS2971A、GS2972芯片引出SDI視頻輸入、輸出案例。通過GTX高速串行總線引出的SDI視頻輸入、輸出案例即將發(fā)布,敬請(qǐng)期待。

案例功能:評(píng)估板通過FMC視頻模塊TL2971A/2972F的SDI IN接口進(jìn)行1080P60視頻采集,并通過TL2971A/2972F模塊的SDI OUT接口將采集到的視頻進(jìn)行輸出。

3 案例演示

將創(chuàng)龍科技的TL2971A/2972F模塊連接至評(píng)估板FMC1接口,評(píng)估板J1跳線帽選擇3.3V檔位,以配置FMC IO的BANK電壓為3.3V。

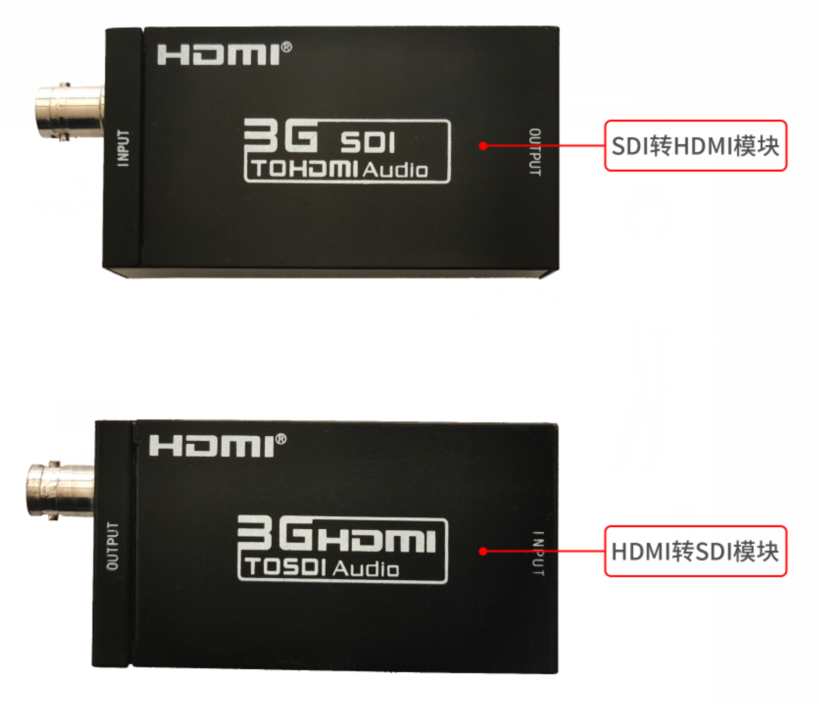

準(zhǔn)備一臺(tái)擁有HDMI OUT接口的PC機(jī)(例如筆記本),通過HDMI數(shù)據(jù)線將PC機(jī)HDMI OUT接口連接至HDMI轉(zhuǎn)SDI模塊(廠家:玩視,型號(hào):3G HDMI TO SDI Audio)INPUT接口,PC機(jī)HDMI OUT接口用作圖像輸出。通過SDI數(shù)據(jù)線將TL2971A/2972F模塊的SDI IN接口連接至HDMI轉(zhuǎn)SDI模塊的OUTPUT接口。

通過SDI數(shù)據(jù)線將TL2971A/2972F模塊的SDI OUT接口連接至SDI轉(zhuǎn)HDMI模塊(廠家:玩視,型號(hào):3G SDI TO HDMI Audio)的INPUT接口,再通過HDMI數(shù)據(jù)線將一臺(tái)HDMI顯示屏連接至SDI轉(zhuǎn)HDMI模塊的OUTPUT接口,HDMI顯示屏用作圖像顯示。

圖6

圖7

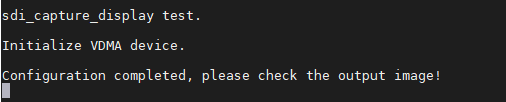

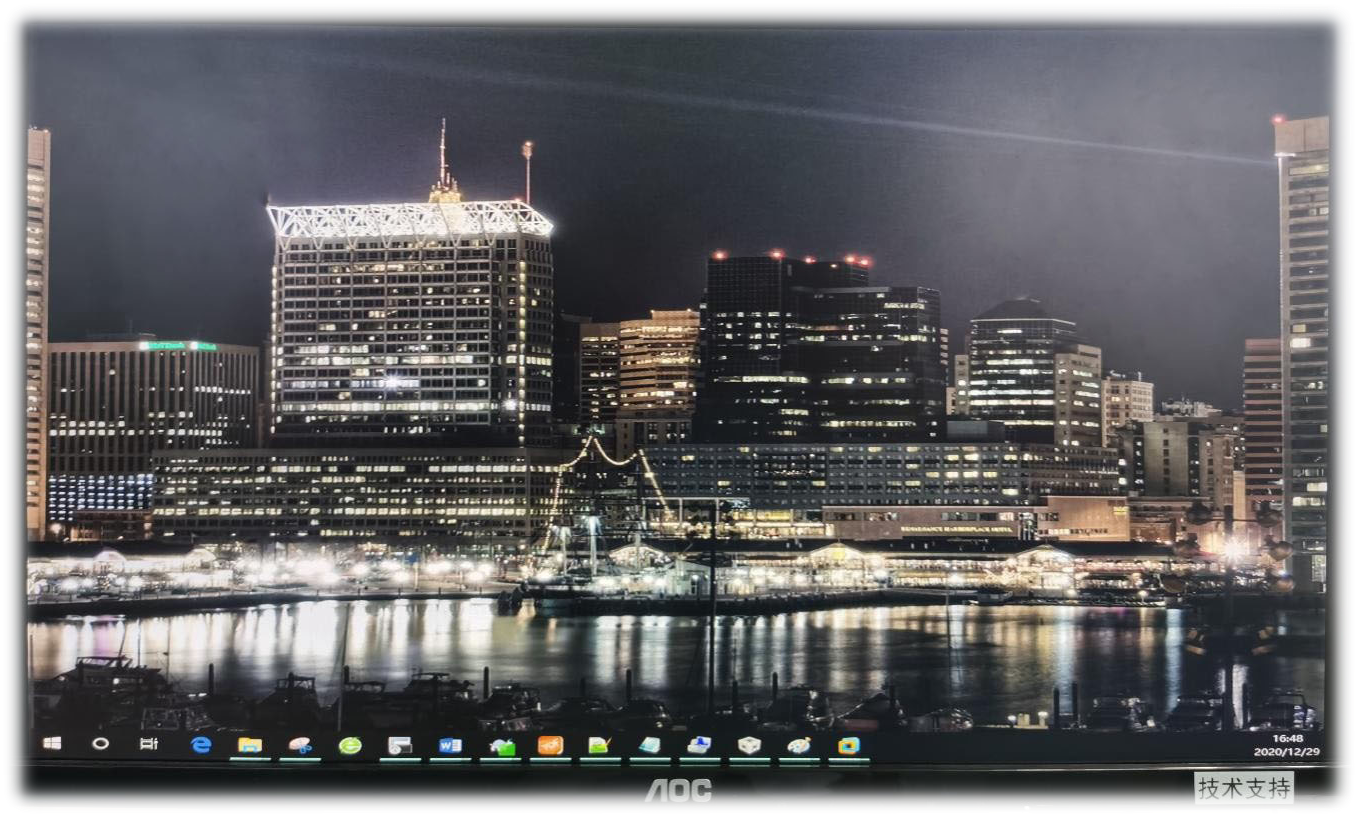

運(yùn)行程序,即可看到串口調(diào)試終端打印如下信息,然后在PC機(jī)的顯卡設(shè)置(或圖形屬性)中,按照下圖設(shè)置HDMI分辨率為1920x1080、刷新率為60pHz。

圖8

圖9

此時(shí),HDMI顯示屏將顯示PC機(jī)HDMI OUT接口輸出的圖像。

圖10

圖11

4 關(guān)鍵代碼(MicroBlaze)

MicroBlaze裸機(jī)源碼為"sw\baremetal_demo\project\sdi_capture_display\src\",關(guān)鍵代碼說明如下。

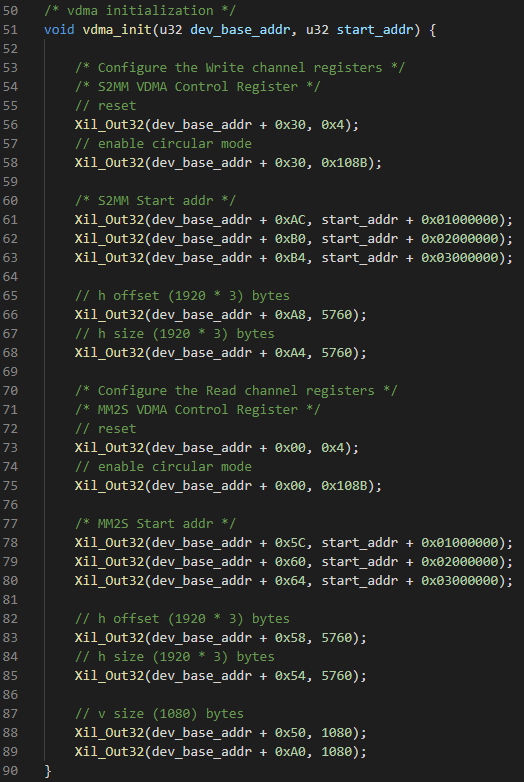

(1) 初始化VDMA,將采集到的視頻數(shù)據(jù)緩存至DDR,并將視頻數(shù)據(jù)搬運(yùn)至AXI4-Stream to Video Out IP核,再進(jìn)行SDI視頻輸出。

圖12

5 Vivado工程說明

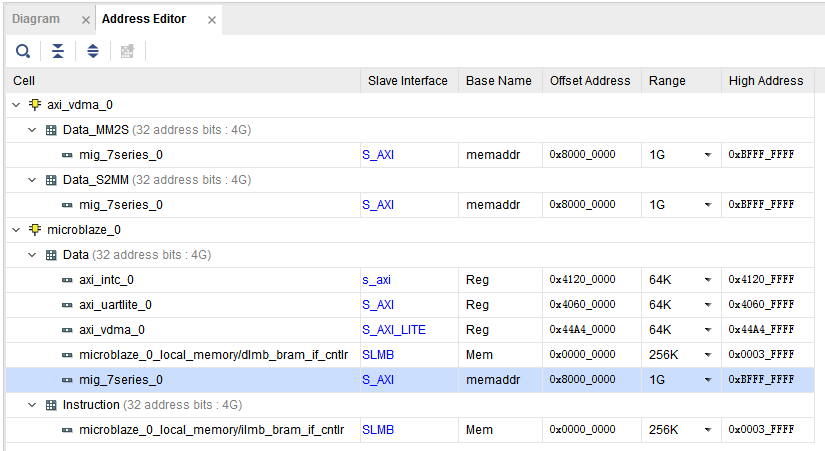

點(diǎn)擊BLOCK DESIGN開發(fā)界面下的"Address Editor"選項(xiàng),可查看IP核分配的地址,MicroBlaze可通過對(duì)應(yīng)地址對(duì)IP核進(jìn)行控制。

圖13

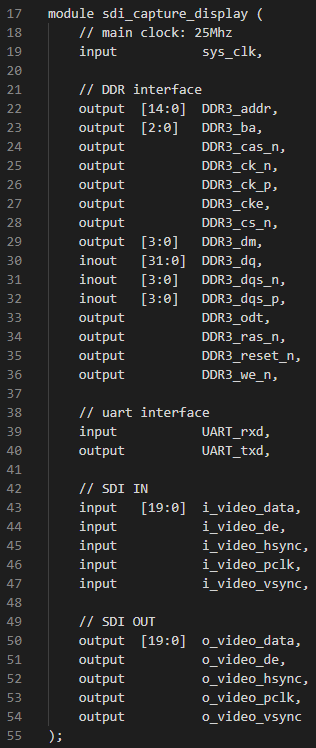

Vivado工程頂層文件為"hw\project\sdi_capture_display.srcs\sources_1\imports\hdl\sdi_capture_display.v",關(guān)鍵代碼說明如下。

(1) 定義模塊接口。

圖14

(2) 使用STARTUPE2原語輸出復(fù)位信號(hào)。

![]()

圖15

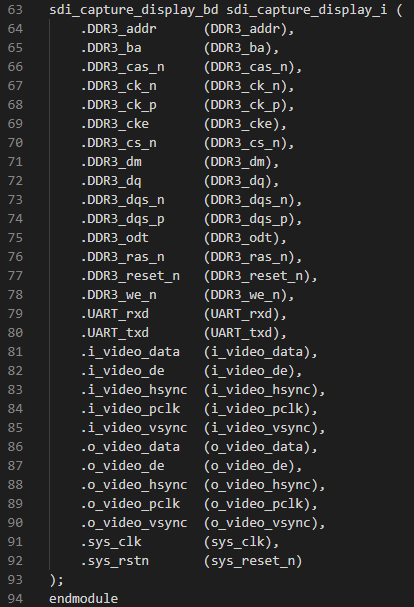

(3) 調(diào)用Block Design。

圖16

6 IP核配置

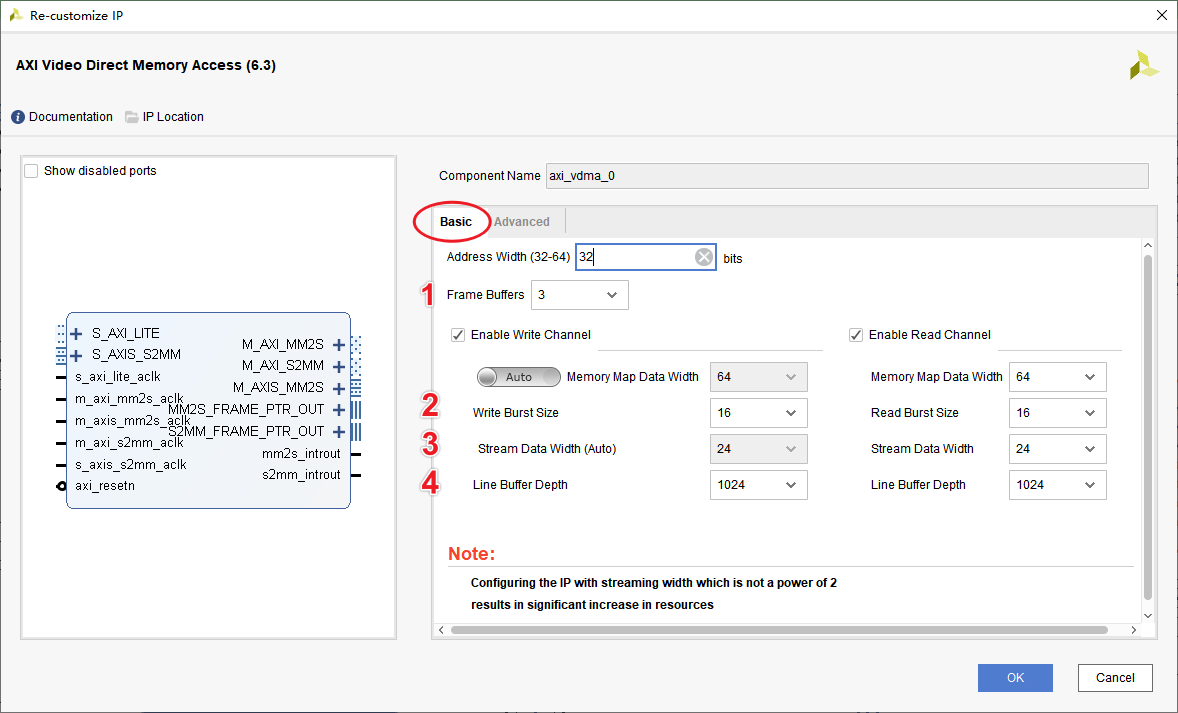

6.1 VDMA IP核

本案例使用VDMA IP核進(jìn)行視頻數(shù)據(jù)緩存。

VDMA(AXI Video Direct Memory Access) IP核開發(fā)文檔為產(chǎn)品資料“6-開發(fā)參考資料\Xilinx官方參考文檔\”目錄下的pg020_axi_vdma.pdf,具體配置說明如下。

(1) Frame Buffer配置為3個(gè)。

(2) Write Burst Size、Read Burst Size均配置為16。

(3) 讀通道的Stream Date Width配置為24。

(4) 讀/寫通道的Line Buffer Depth均配置為1024。

圖17

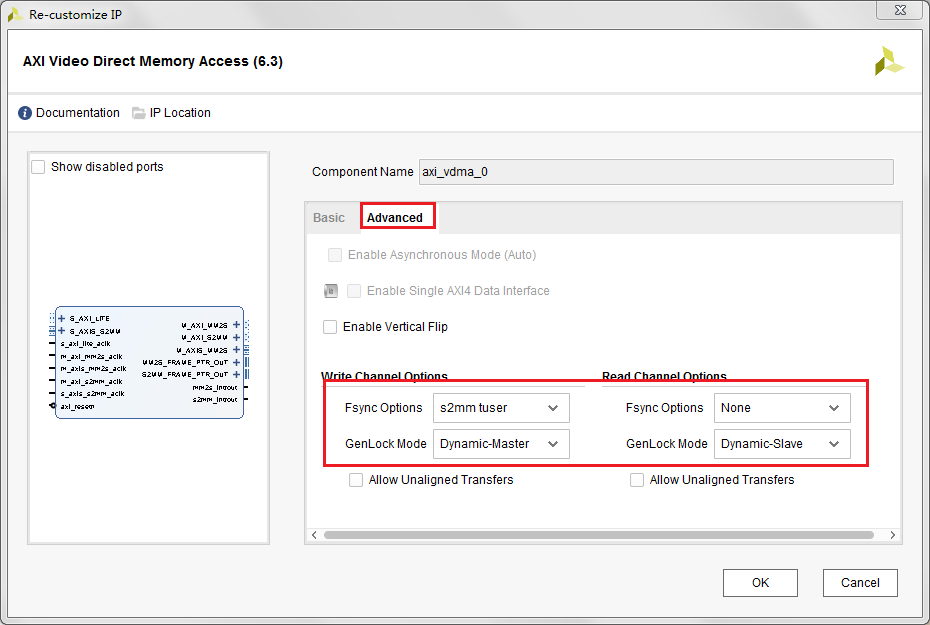

(5) 點(diǎn)擊Advanced,保持默認(rèn)配置,即可避免VDMA同時(shí)讀寫同一個(gè)Buffer,造成視頻數(shù)據(jù)傳輸亂碼。

圖18

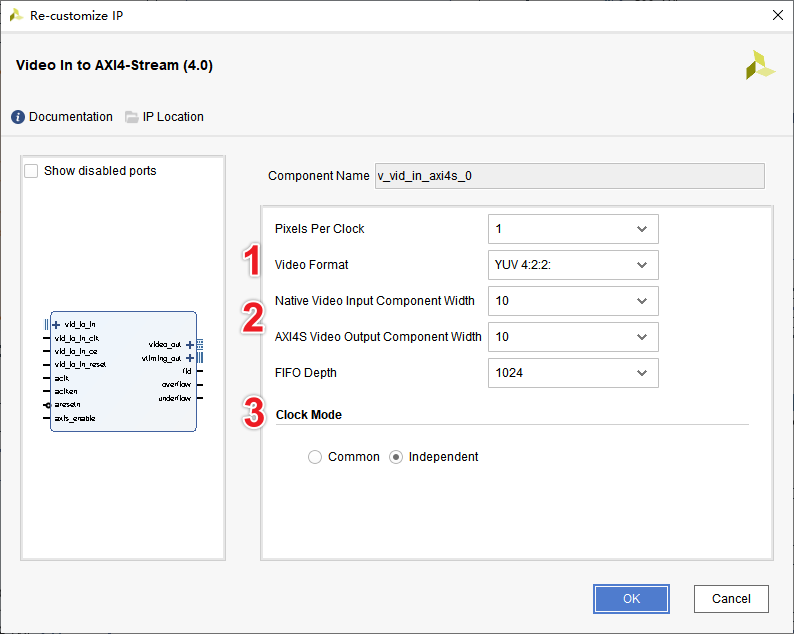

6.2 Video In to AXI4-Stream IP核

本案例使用Video In to AXI4-Stream IP核將并行視頻信號(hào)轉(zhuǎn)換為AXI4-Stream視頻流。

Video In to AXI4-Stream IP核開發(fā)文檔為產(chǎn)品資料“6-開發(fā)參考資料\Xilinx官方參考文檔\”目錄下的《pg043_v_vid_in_axi4s.pdf》,具體配置說明如下。

(1) 視頻格式配置為YUV 4:2:2。

(2) 數(shù)據(jù)位寬配置為10bit。

(3) Clock Mode配置為Independent(獨(dú)立時(shí)鐘)。

圖19

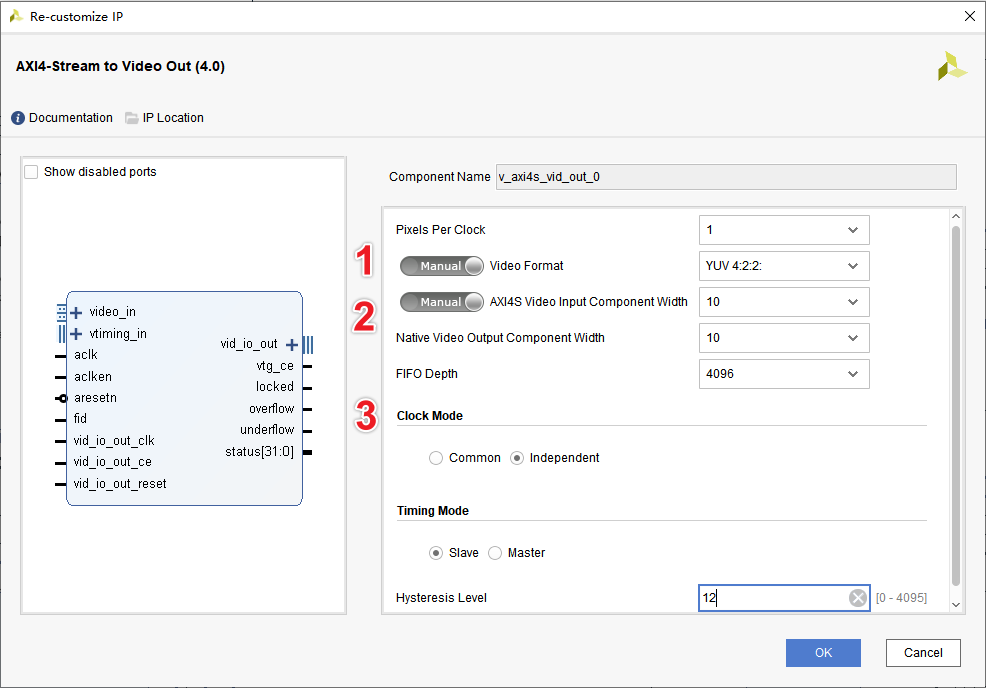

6.3 AXI4-Stream to Video Out IP核

本案例使用AXI4-Stream to Video Out IP核將AXI4-Stream視頻流轉(zhuǎn)化為并行視頻信號(hào)。

AXI4-Stream to Video Out IP核開發(fā)文檔為產(chǎn)品資料“6-開發(fā)參考資料\Xilinx官方參考文檔\”目錄下的《pg044_v_axis_vid_out.pdf》,具體配置說明如下。

(1) 視頻格式配置為YUV 4:2:2。

(2) 數(shù)據(jù)位寬配置為10bit。

(3) Clock Mode配置為Independent(獨(dú)立時(shí)鐘)。

圖20

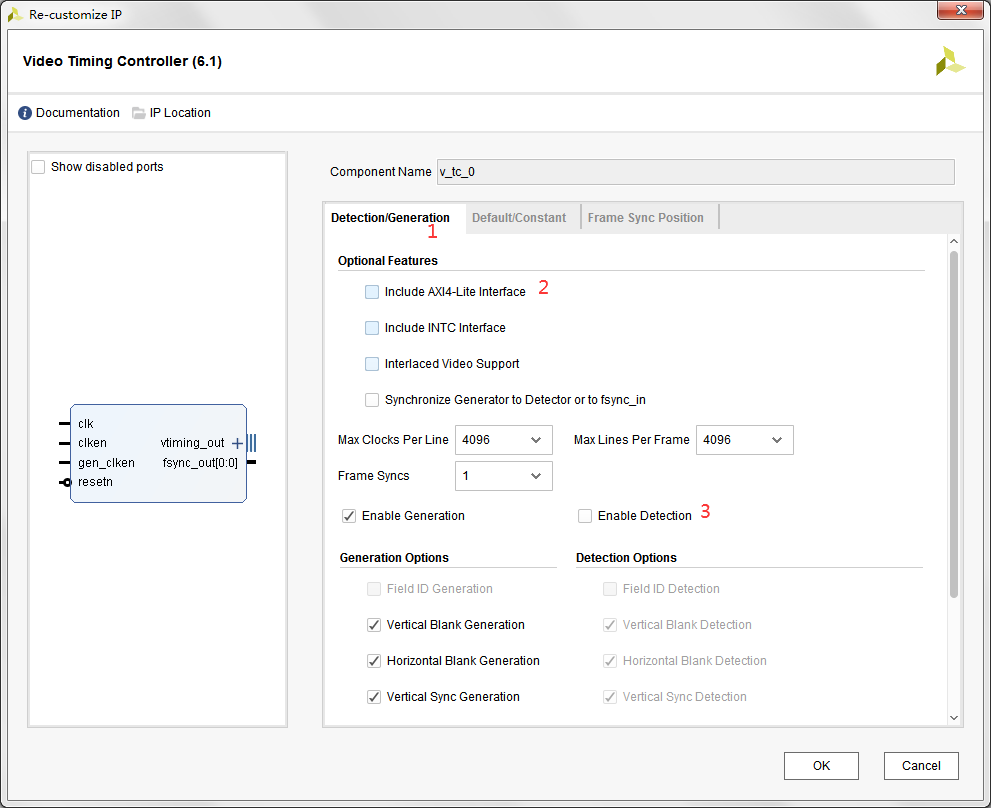

6.4 VTC IP核

本案例使用VTC IP核產(chǎn)生用于視頻輸出的時(shí)序。

VTC(Video Timing Controller) IP核開發(fā)文檔為產(chǎn)品資料“6-開發(fā)參考資料\Xilinx官方參考文檔\”目錄下的《pg016_v_tc.pdf》,具體配置說明如下。

(1) 點(diǎn)擊Detection/Generation,確保不勾選"Include AXI4-Lite Interface"及"Enable Detection"。

圖21

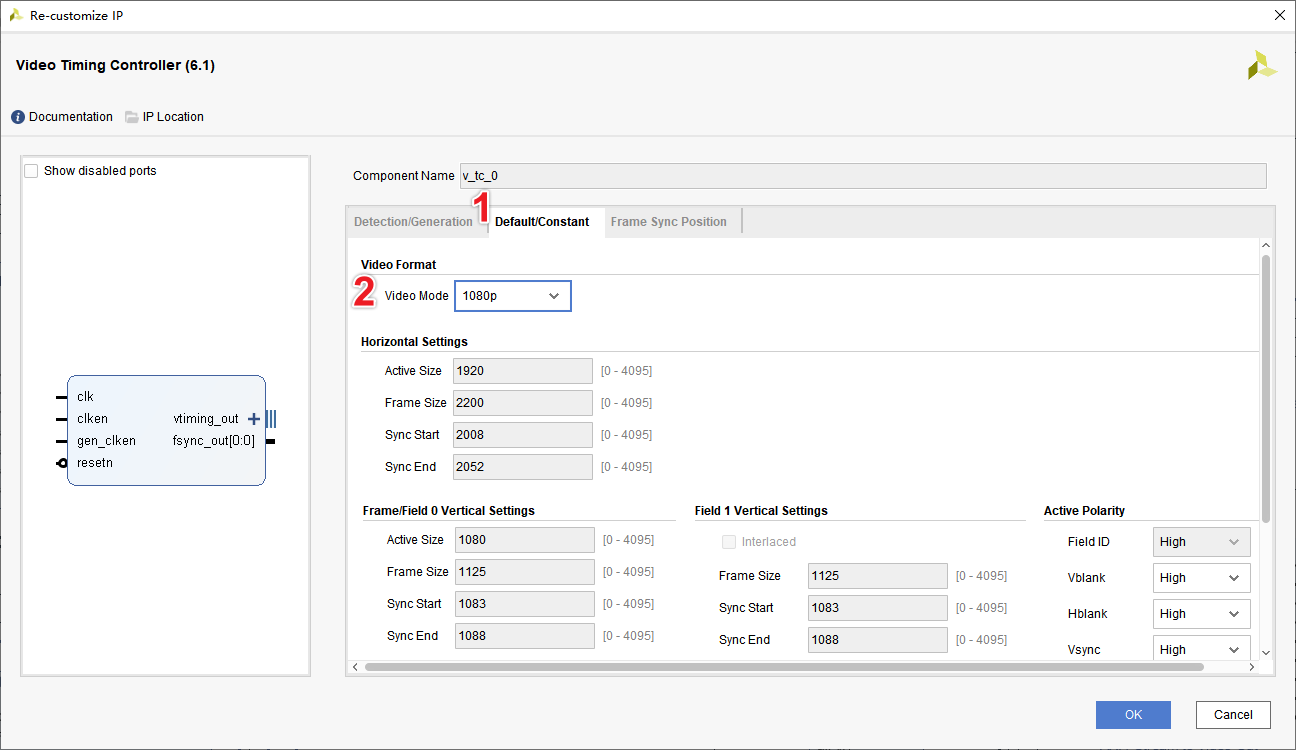

(2) 點(diǎn)擊Default/Constant,Video Mode設(shè)為1080p,其余配置保持默認(rèn)。

圖22

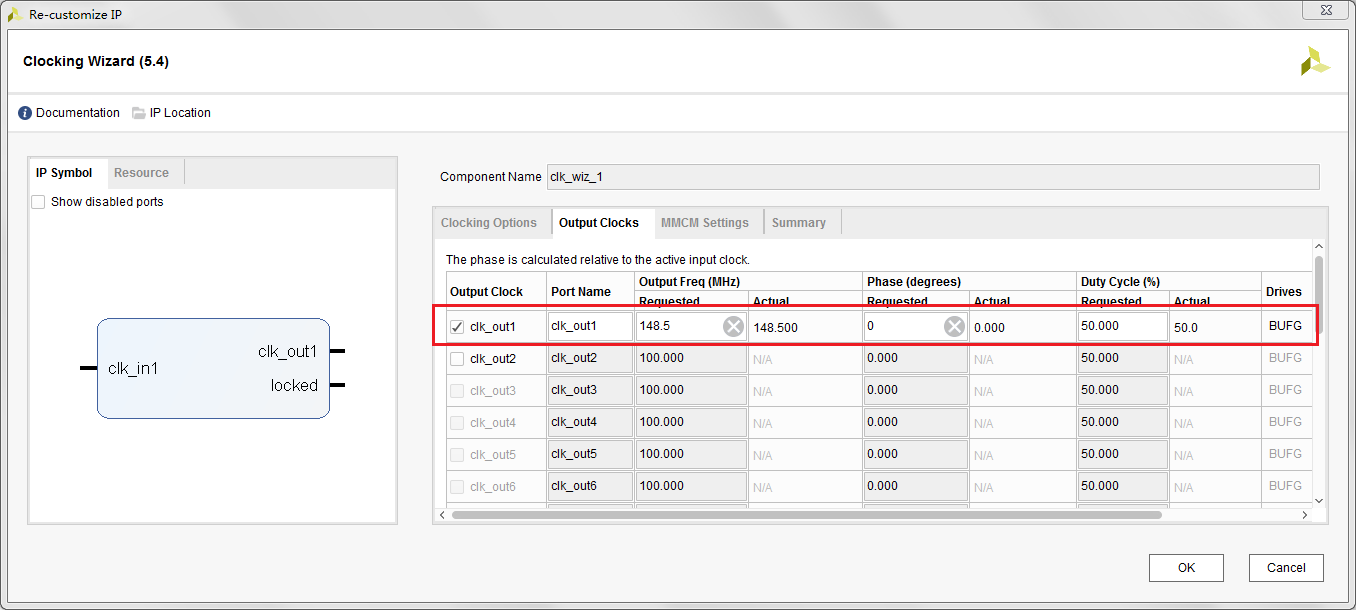

6.5 Clocking Wizard IP核

本案例使用Clocking Wizard IP核產(chǎn)生用于視頻輸出的像素時(shí)鐘(148.5MHz,對(duì)應(yīng)1080P60)。

Clocking Wizard IP核開發(fā)文檔為產(chǎn)品資料“6-開發(fā)參考資料\Xilinx官方參考文檔\”目錄下的《pg065-clk-wiz.pdf》,具體配置如下。

圖23

7 技術(shù)交流群

Kintex-7 FPGA交流群:311416997、101245165

Zynq-7000交流群:645235672、193393878

8 更多推薦

服務(wù)熱線

服務(wù)熱線