聯(lián)系我們

Contact Us公司總機(jī):020-8998-6280

技術(shù)熱線:020-3893-9734

技術(shù)郵箱:support@tronlong.com

銷(xiāo)售郵箱:sales@tronlong.com

一文讀懂DSP C66x多核開(kāi)發(fā)

2021/01/14

前言

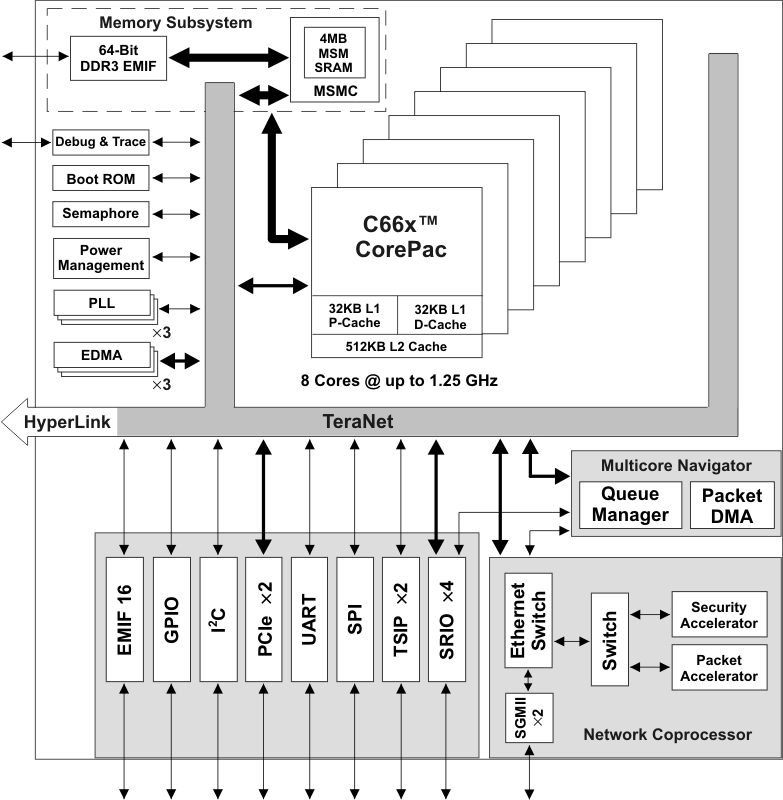

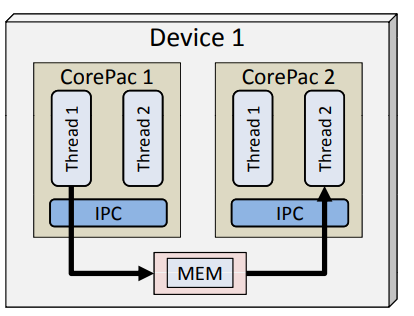

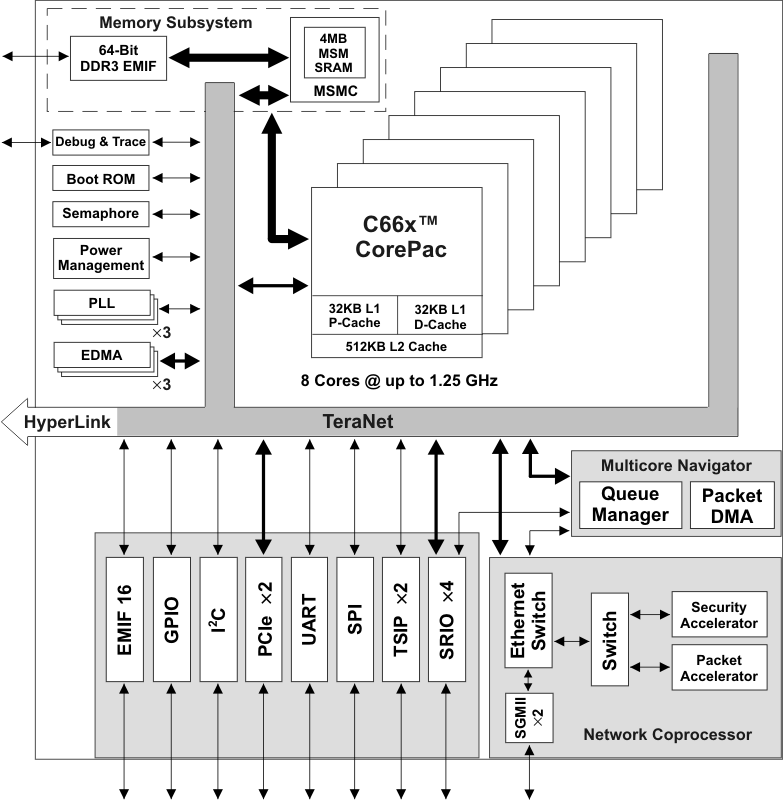

嵌入式領(lǐng)域的處理器已向多核架構(gòu)迅速發(fā)展,TI公司的KeyStone架構(gòu)的TMS320C6678是目前市面上性能最高的多核DSP處理器。TMS320C6678集成8核C66x DSP處理器,每個(gè)內(nèi)核頻率高達(dá)1.25 GHz,提供每秒高達(dá)40 GMAC定點(diǎn)運(yùn)算和20 GFLOP浮點(diǎn)運(yùn)算能力;1片TMS320C6678提供等效達(dá)10 GHz的內(nèi)核頻率,單精度浮點(diǎn)并行運(yùn)算能力理論上可達(dá)160 GFLOP,是TS201S的50倍、C67x+的115.2倍,適合于諸如油氣勘探、雷達(dá)信號(hào)處理、圖像處理以及定位導(dǎo)航等對(duì)定浮點(diǎn)運(yùn)算能力及實(shí)時(shí)性有較高要求的超高性能計(jì)算應(yīng)用。

然而,核間通信是多核處理器系統(tǒng)所面臨的主要難點(diǎn),通信機(jī)制的優(yōu)劣直接影響多核處理器的性能,高效的通信機(jī)制是發(fā)揮多核處理器高性能的重要保障。

創(chuàng)龍科技(Tronlong)專(zhuān)注于DSP、ARM、FPGA多核異構(gòu)技術(shù)開(kāi)發(fā),本文為您介紹TMS320C6678處理器開(kāi)發(fā)中比較常用的兩種多核通信方式:TI-IPC和OpenMP,以及多核編程注意事項(xiàng)。

1 硬件平臺(tái)

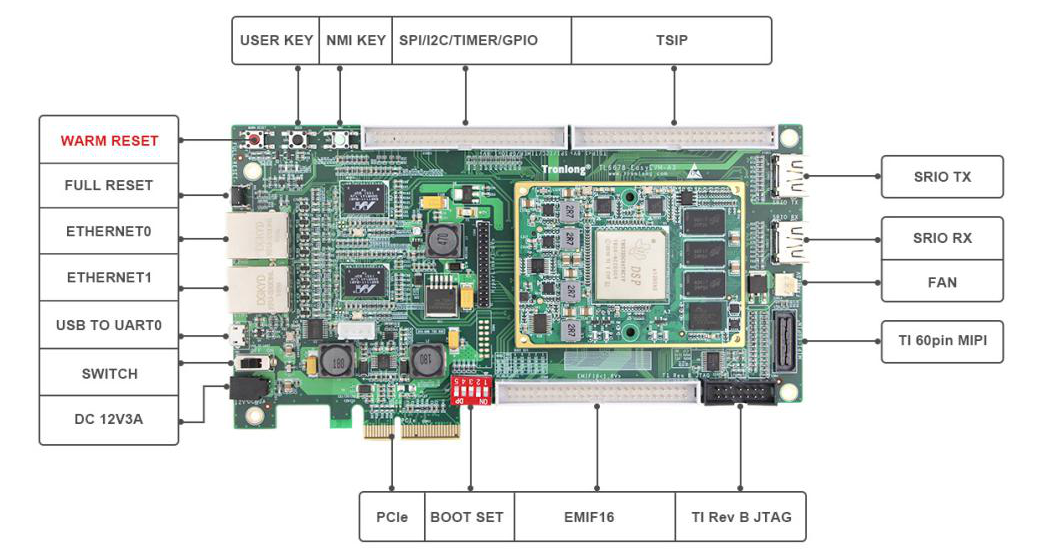

本文基于創(chuàng)龍科技TL6678-EasyEVM評(píng)估板進(jìn)行演示。

TL6678-EasyEVM是一款基于TI KeyStone架構(gòu)C6000系列TMS320C6678八核C66x定點(diǎn)/浮點(diǎn)高性能處理器設(shè)計(jì)的高端多核DSP評(píng)估板,由核心板與底板組成。核心板經(jīng)過(guò)專(zhuān)業(yè)的PCB Layout和高低溫測(cè)試驗(yàn)證,穩(wěn)定可靠,可滿足各種工業(yè)應(yīng)用環(huán)境。

評(píng)估板接口資源豐富,引出雙路千兆網(wǎng)口、SRIO、PCIe等高速通信接口,方便用戶(hù)快速進(jìn)行產(chǎn)品方案評(píng)估與技術(shù)預(yù)研。

TL6678-EasyEVM評(píng)估板

開(kāi)發(fā)案例主要包括:

(1) 裸機(jī)開(kāi)發(fā)案例

(2) RTOS(SYS/BIOS)開(kāi)發(fā)案例

(3) IPC、OpenMP多核開(kāi)發(fā)案例

(4) SRIO、PCIe、雙千兆網(wǎng)口開(kāi)發(fā)案例

(5) 圖像處理開(kāi)發(fā)案例

(6) DSP算法開(kāi)發(fā)案例

(7) 串口、網(wǎng)絡(luò)遠(yuǎn)程升級(jí)開(kāi)發(fā)案例

C66x DSP視頻教程、中文手冊(cè)、產(chǎn)品資料(用戶(hù)手冊(cè)、核心板硬件資料、產(chǎn)品規(guī)格書(shū))可點(diǎn)擊下方鏈接或掃碼二維碼獲取。

http://site.tronlong.com/pfdownload

2 TI-IPC

2.1 簡(jiǎn)介

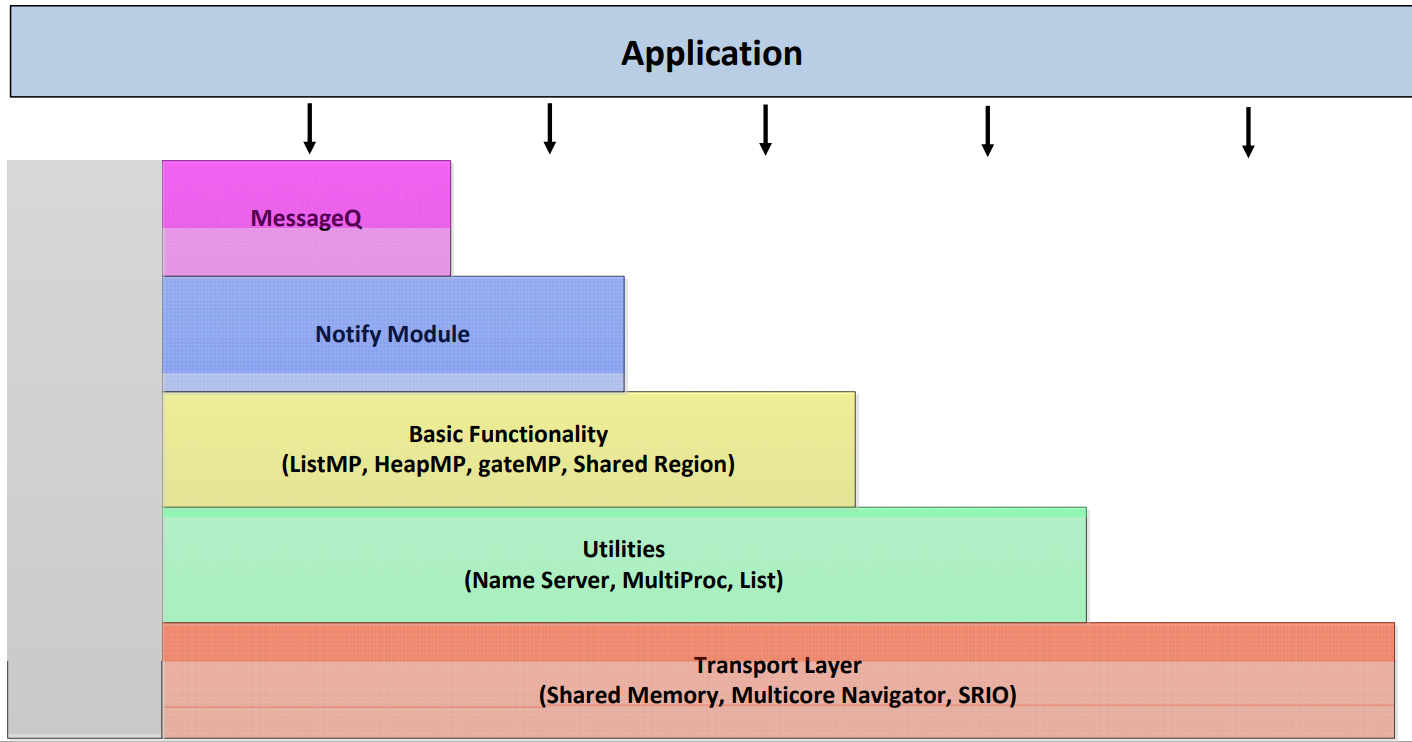

TI-IPC(Inter-Processor Communication)組件提供與處理器硬件無(wú)關(guān)的API,可用于多核處理器核間通信、同一處理器進(jìn)程間通信和設(shè)備間通信。API支持消息傳遞、流和鏈接列表,它們?cè)趩翁幚砥骱投嗵幚砥髦信渲镁杉嫒荨?/span>

TI-IPC被設(shè)計(jì)在運(yùn)行SYS/BIOS應(yīng)用程序的處理器上使用,一般為DSP處理器(如TMS320C6678、TMS320C6657),但在某些情況下亦可能是ARM處理器。

|

Ipc |

提供Ipc_start()函數(shù),并允許配置啟動(dòng)順序 |

|

MessageQ |

大小可變的消息傳遞模塊 |

|

Notify |

以中斷方式實(shí)現(xiàn)輕量數(shù)據(jù)傳輸?shù)哪K |

|

ListMp |

用于實(shí)現(xiàn)對(duì)鏈接列表的互斥訪問(wèn) |

|

GateMp |

用于實(shí)現(xiàn)對(duì)共享資源的互斥訪問(wèn) |

|

HeapBufMp |

大小固定的共享內(nèi)存堆 |

|

HeapMenMp |

大小可變的共享內(nèi)存堆 |

|

SharedRegion |

用于維護(hù)共享內(nèi)存區(qū)域 |

|

List |

用于創(chuàng)建雙向鏈接列表 |

|

MultiProc |

用于管理多核處理器核心ID |

|

NameServer |

用于應(yīng)用程序基于本地名稱(chēng)檢索,以及存儲(chǔ)變量值 |

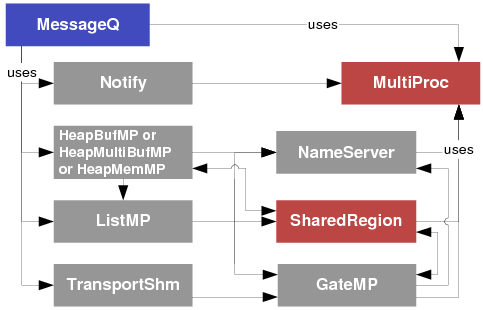

2.2 常用模塊

2.2.1 MessageQ

該模塊具有如下特點(diǎn):

(1) 兼容性強(qiáng),可在不更改運(yùn)行代碼的情況移植至另一個(gè)支持TI-IPC MessageQ的處理器或其他傳輸層(如Shared Memory、Multicore Navigator、SRIO)。

(2) 支持可變長(zhǎng)度消息的結(jié)構(gòu)化發(fā)送與接收。

(3) 單個(gè)MessageQ隊(duì)列支持單個(gè)reader和多個(gè)writer。

(4) 消息接收支持超時(shí)機(jī)制。

(5) reader可根據(jù)消息頭部信息對(duì)writer進(jìn)行確認(rèn)后再回復(fù)。

(6) Ipc_start()會(huì)幫助用戶(hù)完成下圖中灰色框內(nèi)的功能,用戶(hù)僅需關(guān)注紅色框中的內(nèi)容即可。

MessageQ通過(guò)消息隊(duì)列發(fā)送和接收消息。reader是一個(gè)從消息隊(duì)列中讀取消息的線程,writer是一個(gè)將消息寫(xiě)入消息隊(duì)列的線程。每個(gè)消息隊(duì)列都有一個(gè)reader,但可有多個(gè)writer。

■ reader:調(diào)用MessageQ_create()、MessageQ_get()、MessageQ_free()和MessageQ_delete()。

■ writer:調(diào)用MessageQ_open()、MessageQ_alloc()、MessageQ_put()和MessageQ_close()。

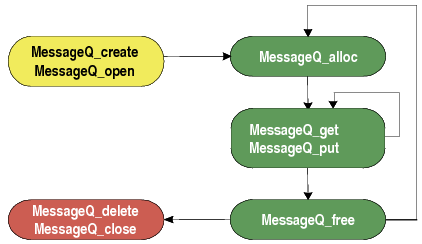

MessageQ常見(jiàn)的工作流程如下所示。

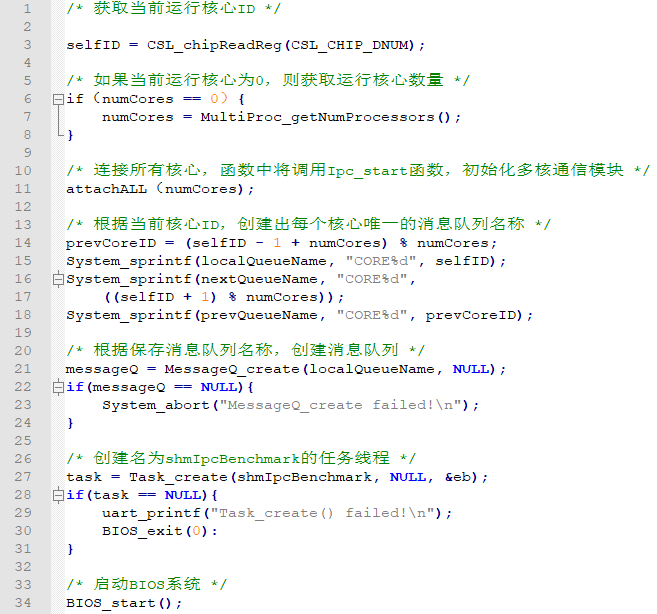

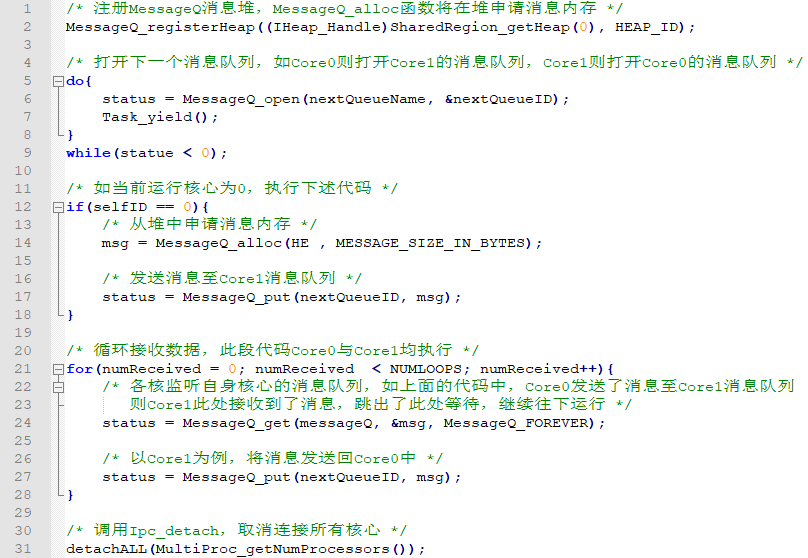

下面以多核IPC通信的shmIpcBenchmark案例為例,分析代碼中MessageQ的使用,見(jiàn)圖中注釋。

2.2.2 Notify

該模塊具有如下特點(diǎn):

(1) 可獨(dú)立于MessageQ模塊進(jìn)行使用。

(2) 著重于多核通知功能,是更為簡(jiǎn)單的多核通信形式。

(3) 僅可基于Shared Memroy方式進(jìn)行使用。

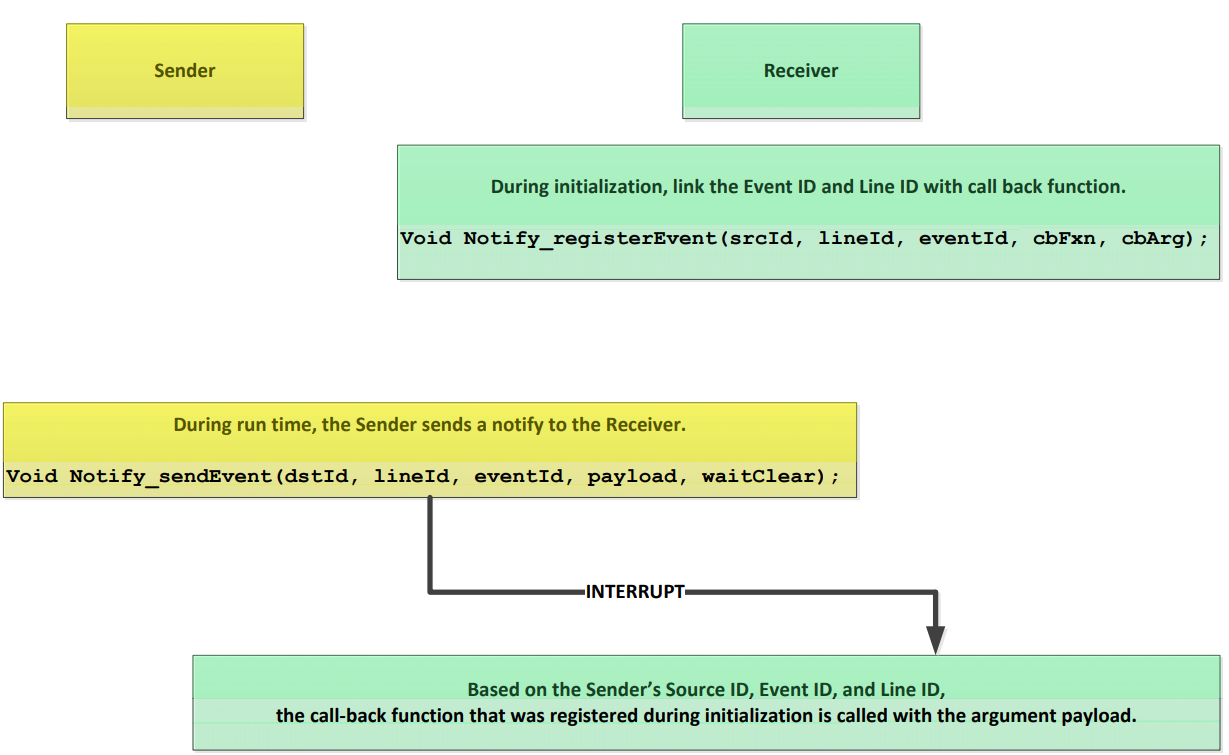

Notify通過(guò)硬件中斷傳輸消息,Receiver注冊(cè)Notify事件中斷,Sender通過(guò)Notify發(fā)送事件中斷,從而實(shí)現(xiàn)通知并攜帶小量消息的目的。

■ Receiver:調(diào)用Notify_registerEvent()注冊(cè)事件中斷服務(wù)函數(shù)。

■ Sender:調(diào)用Notify_sendEvent()發(fā)送事件中斷。

Notify常見(jiàn)的工作流程如下所示。

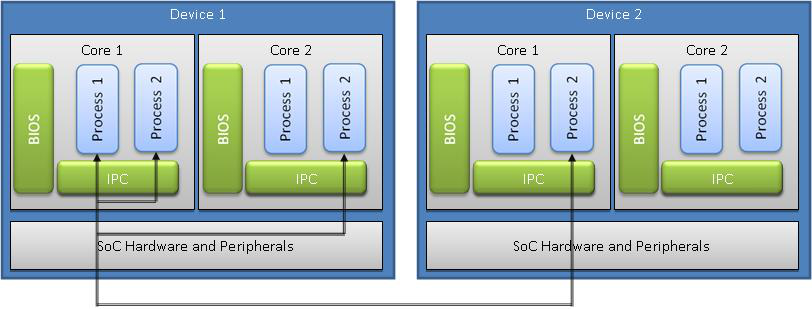

2.3 物理傳輸方式

TI-IPC的數(shù)據(jù)傳輸需結(jié)合特定物理硬件與底層驅(qū)動(dòng),方可實(shí)現(xiàn)兩個(gè)線程在同一個(gè)設(shè)備或跨設(shè)備間進(jìn)行通信。常用三種的物理傳輸方式包括Shared Memory、Multicore Navigator和SRIO,具體說(shuō)明如下。

表2

|

傳輸方式 |

優(yōu)點(diǎn) |

缺點(diǎn) |

|

Shared Memory |

使用簡(jiǎn)單,速率較高 |

僅可用于單個(gè)設(shè)備IPC通信,可能與其他使用Shared Memory的任務(wù)存在競(jìng)爭(zhēng) |

|

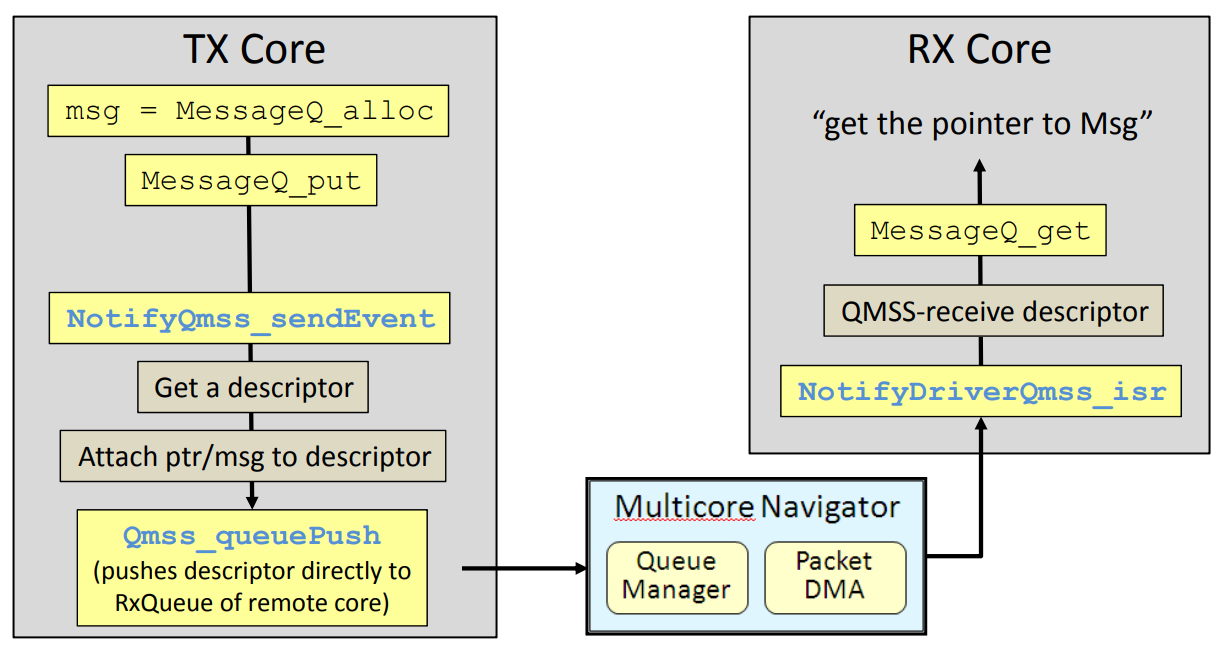

Multicore Navigator |

速率最高,消耗CPU周期最少 |

僅可用于單個(gè)設(shè)備IPC通信 |

|

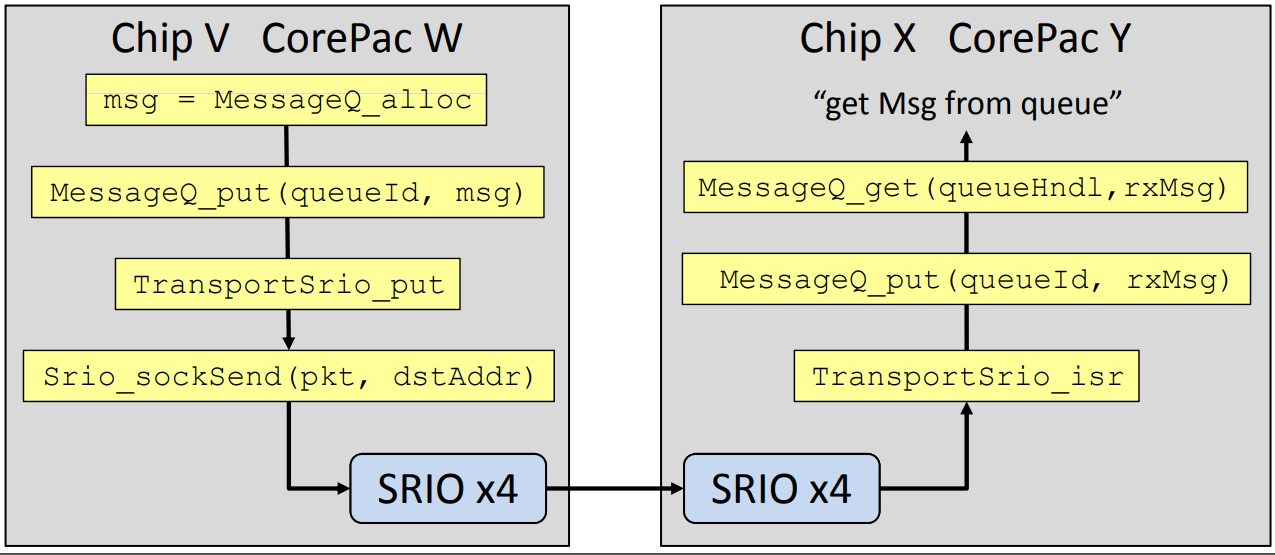

SRIO |

可用于跨設(shè)備IPC通信 |

速率最低 |

下圖為使用Multicore Navigator、SRIO的API調(diào)用流程,用戶(hù)僅需關(guān)注MessageQ部分操作即可,其他模塊均由系統(tǒng)自動(dòng)調(diào)用。

3 OpenMP

3.1 簡(jiǎn)介

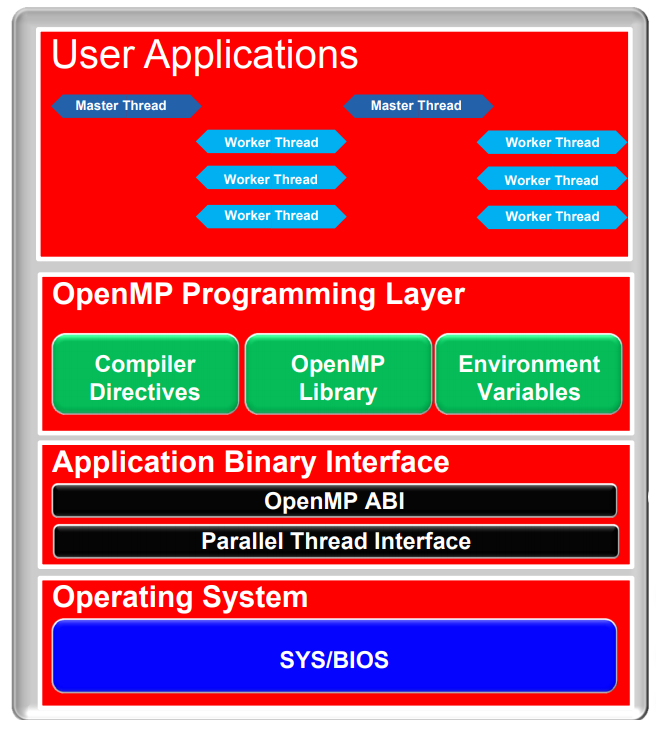

OpenMP是一種多核開(kāi)發(fā)軟件框架,其主要特性如下:

(1) 可跨平臺(tái)使用,代碼兼容性強(qiáng)。

(2) 以共享內(nèi)存為通信基礎(chǔ)。

(3) 支持C/C++以及Fortran語(yǔ)言。

(4) 一般基于SYS/BIOS運(yùn)行。

3.2 基本語(yǔ)法

#pragma omp 指令 [子句 [ [ [,]子句 ] ... ]

{

...

}

表3

|

指令 |

說(shuō)明 |

|

parallel |

開(kāi)始并行執(zhí)行語(yǔ)句 |

|

for |

在多個(gè)線程中并行執(zhí)行for循環(huán) |

|

sections |

包含多個(gè)可并行執(zhí)行的sectone結(jié)構(gòu)體 |

|

single |

單線程執(zhí)行 |

|

master |

主線程執(zhí)行 |

|

critical |

任意時(shí)刻僅可被單個(gè)線程執(zhí)行 |

|

barrier |

指定屏障,用于同步所有線程 |

|

taskwait |

等待子線程完成 |

|

atomic |

確保指定內(nèi)存位置執(zhí)行原子更新操作 |

|

flush |

使線程當(dāng)前內(nèi)存數(shù)據(jù)與實(shí)際內(nèi)存數(shù)據(jù)一致 |

|

ordered |

并行執(zhí)行的for循環(huán)將按循環(huán)體變量順序執(zhí)行 |

|

threadprivate |

指定變量為本地存儲(chǔ) |

表4

|

子句 |

說(shuō)明 |

|

default |

控制parallel或task結(jié)構(gòu)體中變量數(shù)據(jù)的共享屬性 |

|

shared |

parallel或task結(jié)構(gòu)中,一個(gè)或多個(gè)變量為共享變量 |

|

private |

一個(gè)或多個(gè)變量為本地變量 |

|

firstprivate |

一個(gè)或多個(gè)變量為本地變量,且變量值為并行結(jié)構(gòu)執(zhí)行前的值 |

|

lastprivate |

一個(gè)或多個(gè)變量為本地變量,且變量值為并行結(jié)構(gòu)執(zhí)行后的值 |

|

reduction |

一個(gè)或多個(gè)變量為本地變量,但變量值將根據(jù)不同的運(yùn)算符來(lái)決定,執(zhí)行完成后變量值將被更新 |

|

copyin |

使線程本地變量值與主線程變量值相同 |

|

copyprivate |

使屬于parallel區(qū)域的變量值在不同線程中相同 |

|

schedule |

設(shè)置for循環(huán)并行執(zhí)行方式:dynamic、guided、runtime和static |

|

num_threads |

線程數(shù)目 |

|

if |

并行語(yǔ)句執(zhí)行條件 |

|

nowait |

忽略線程同步等待 |

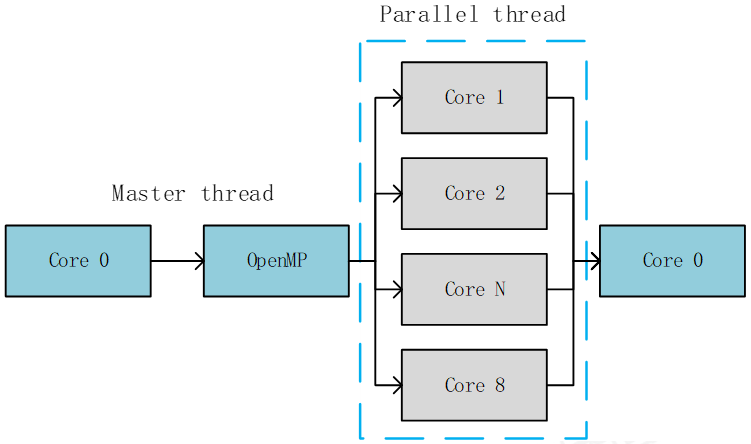

以裸機(jī)的omp_matavec案例為例,使用場(chǎng)景的概要流程圖如下。

C66xx_0核心創(chuàng)建主線程,通過(guò)OpenMP框架加載matvec算法至C66xx_0~C66xx_7核心進(jìn)行并行運(yùn)算,從而減少C66xx_0核心負(fù)載,并可加快運(yùn)算速度。

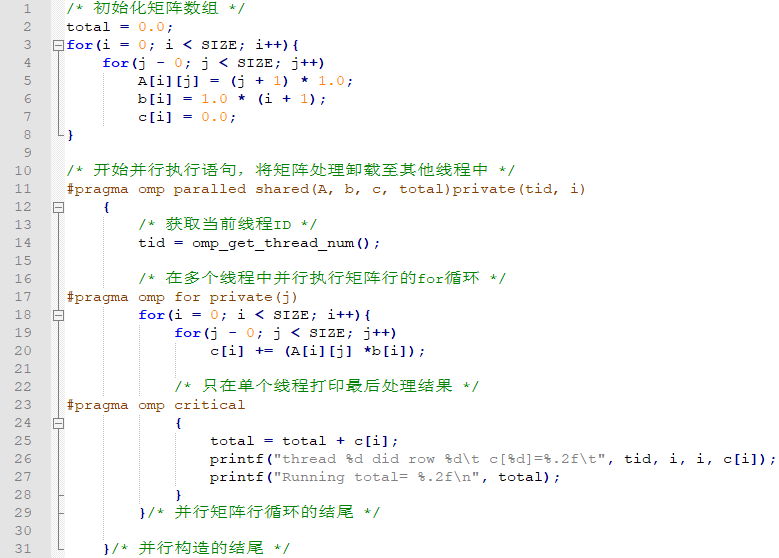

3.3 代碼分析

以裸機(jī)的omp_matavec案例為例進(jìn)行代碼分析,見(jiàn)圖中注釋。

4 多核編程注意事項(xiàng)

4.1 多核單/多鏡像

在開(kāi)發(fā)過(guò)程中,需將程序可執(zhí)行文件分別加載至對(duì)應(yīng)的核心運(yùn)行。此時(shí)需了解多核單/多鏡像的優(yōu)缺點(diǎn),再根據(jù)實(shí)際情況進(jìn)行選擇。

多核單鏡像

多核單鏡像指所有核心運(yùn)行完全相同的用戶(hù)程序。

優(yōu)點(diǎn):僅需維護(hù)一個(gè)工程,管理便捷。

缺點(diǎn):需兼容多個(gè)核心代碼,程序可執(zhí)行文件較大。

多核多鏡像

多核多鏡像指不同核心運(yùn)行不同的用戶(hù)程序。

優(yōu)點(diǎn):無(wú)需考慮各核心功能的兼容性,單個(gè)程序可執(zhí)行文件較小。

缺點(diǎn):需維護(hù)多個(gè)工程,管理不便。

4.2 外設(shè)訪問(wèn)

所有核心共享外設(shè),如SRIO、PCIe、Ethernet、SPI、I2C、EMIF等。在對(duì)外設(shè)進(jìn)行初始化后,所有核心可在任意時(shí)間對(duì)外設(shè)進(jìn)行讀寫(xiě),無(wú)需再次初始化。

4.3 數(shù)據(jù)存儲(chǔ)

L1/L2SRAM有全局與局部?jī)蓚€(gè)地址,全局地址可被所有核心訪問(wèn),但局部地址僅可被指定核心訪問(wèn)。

以C66xx_0核心的L2SRAM為例,對(duì)應(yīng)的全局地址為0x10800000,局部地址為0x00800000。C66xx_0核心使用0x10800000或0x00800000,均可訪問(wèn)C66xx_0核心的L2SRAM。而C66xx_1核心使用0x00800000僅可訪問(wèn)C66xx_1核心的L2SRAM,使用0x10800000方可訪問(wèn)C66xx_0核心的L2SRAM。

L2SRAM全局與局部地址對(duì)應(yīng)關(guān)系如下表:

|

核心 |

全局地址 |

局部地址 |

|

C66xx_0 |

0x10800000 |

0x00800000 |

|

C66xx_1 |

0x11800000 |

0x00800000 |

|

C66xx_2 |

0x12800000 |

0x00800000 |

|

C66xx_3 |

0x13800000 |

0x00800000 |

|

C66xx_4 |

0x14800000 |

0x00800000 |

|

C66xx_5 |

0x15800000 |

0x00800000 |

|

C66xx_6 |

0x16800000 |

0x00800000 |

|

C66xx_7 |

0x17800000 |

0x00800000 |

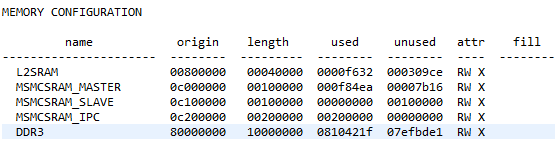

如數(shù)據(jù)需存放至MSMCSRAM、DDR3共享內(nèi)存設(shè)備,請(qǐng)將對(duì)應(yīng)內(nèi)存劃分為MSMCSRAM_MASTER段(主核使用)與MSMCSRAM_SLAVE段(從核使用),從而避免運(yùn)行時(shí)內(nèi)存沖突。

5 參考鏈接

https://training.ti.com/system/files/docs/keystone-intro-ipc-slides.pdf

https://processors.wiki.ti.com/index.php/IPC_Users_Guide/MessageQ_Module

-OpenMP

http://processors.wiki.ti.com/index.php/OpenMP_on_C6000

https://processors.wiki.ti.com/index.php/BIOS_MCSDK_2.0_User_Guide#OpenMP

http://community.topcoder.com/tc?module=Static&d1=features&d2=091106

-Multicore Programming Guide

https://www.ti.com/lit/an/sprab27b/sprab27b.pdf

6 免費(fèi)試用

掃描下方二維碼,即可申請(qǐng)TL6678-EasyEVM評(píng)估板進(jìn)行快速評(píng)估,免費(fèi)哦!

7 技術(shù)交流群

TMS320C6678 DSP交流群:79635273、332643352

8 更多推薦

基于IPC、OpenMP的C66x多核開(kāi)發(fā)視頻教程

服務(wù)熱線

服務(wù)熱線