聯(lián)系我們

Contact Us公司總機(jī):020-8998-6280

技術(shù)熱線:020-3893-9734

技術(shù)郵箱:support@tronlong.com

銷售郵箱:sales@tronlong.com

延時(shí)僅4us!最新的全國產(chǎn)RK3568J+FPGA PCIe實(shí)時(shí)通信方案來了

2025/04/09

實(shí)時(shí)通信方案

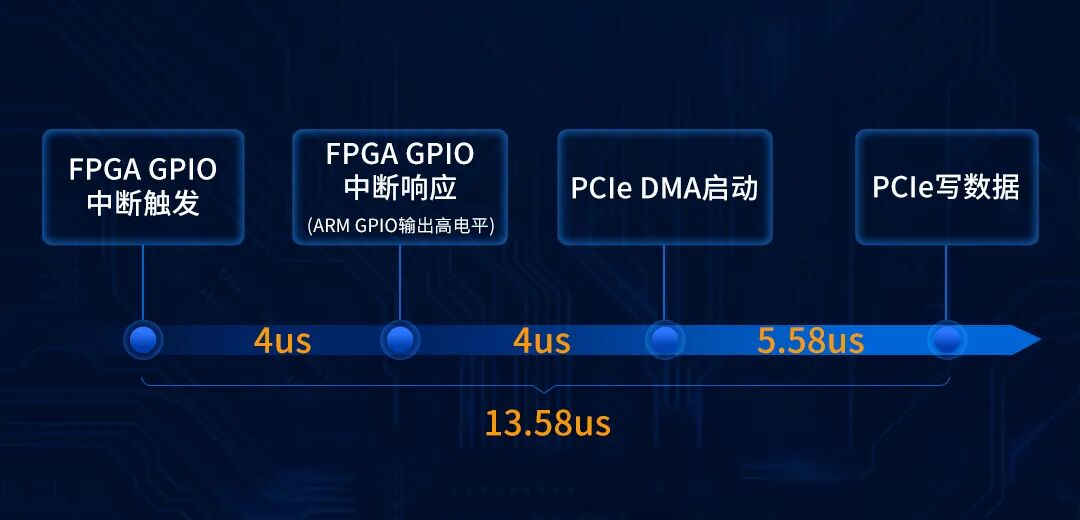

圖 1 中斷響應(yīng)到PCIe通信過程

AMP + GPIO中斷技術(shù)-協(xié)同運(yùn)作

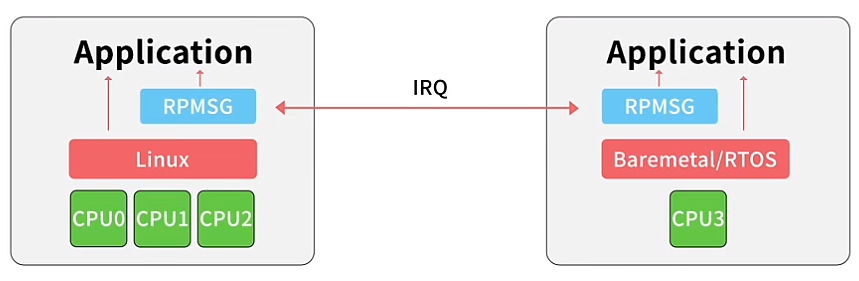

AMP即Asymmetric Multi-Processing,(非對(duì)稱多處理架構(gòu)),多個(gè)核心相對(duì)獨(dú)立運(yùn)行不同的操作系統(tǒng)或裸機(jī)應(yīng)用程序,如Linux+RTOS/裸機(jī)組合。系統(tǒng)需要一個(gè)主核心統(tǒng)籌全局,各處理器核心相互隔離,擁有獨(dú)立內(nèi)存,既能各自執(zhí)行不同任務(wù),又可實(shí)現(xiàn)核間通信。

圖 2

GPIO中斷技術(shù)通過硬件級(jí)事件觸發(fā)機(jī)制,當(dāng)GPIO引腳電平變化,能夠立即中斷處理器當(dāng)前任務(wù),在工業(yè)控制信號(hào)采集、緊急按鍵處理等對(duì)實(shí)時(shí)性要求嚴(yán)苛的場景中表現(xiàn)卓越。

當(dāng)AMP架構(gòu)與GPIO中斷技術(shù)實(shí)現(xiàn)強(qiáng)強(qiáng)聯(lián)合,既能充分發(fā)揮主核調(diào)度與從核實(shí)時(shí)響應(yīng)優(yōu)勢,又可以大幅度提升系統(tǒng)計(jì)算的性能與實(shí)時(shí)性。

DMA技術(shù)-加速數(shù)據(jù)傳輸

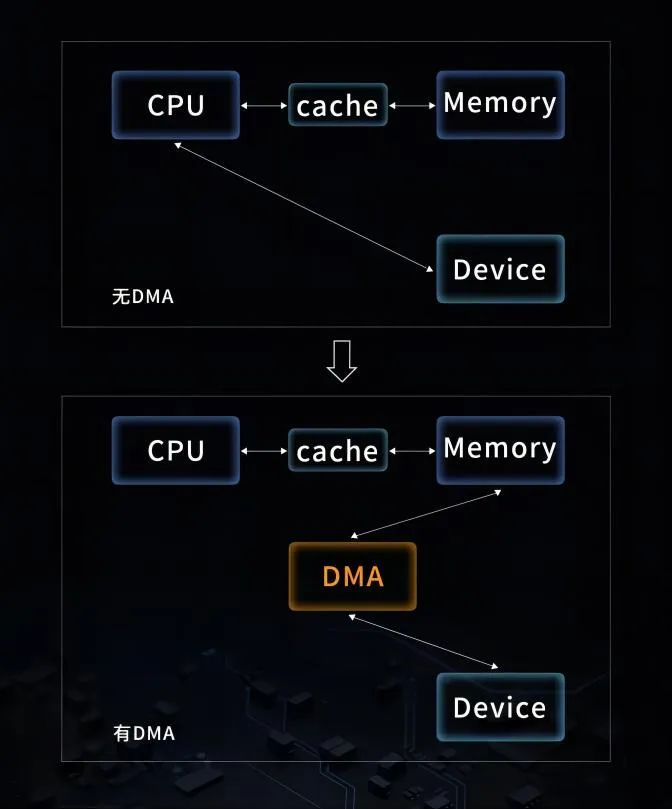

DMA技術(shù)(Direct Memory Access,直接內(nèi)存訪問)允許硬件外設(shè)直接與存儲(chǔ)器進(jìn)行數(shù)據(jù)交換,全程無需CPU參與數(shù)據(jù)傳輸。

使用非DMA方式進(jìn)行數(shù)據(jù)傳輸時(shí),外設(shè)與內(nèi)存之間的數(shù)據(jù)搬運(yùn)需要依靠CPU來完成。這意味著每次數(shù)據(jù)傳輸都需要CPU的介入,導(dǎo)致CPU資源占用較高,并且數(shù)據(jù)傳輸速度相對(duì)較低。而采用DMA方式進(jìn)行數(shù)據(jù)傳輸,外設(shè)可直接與內(nèi)存進(jìn)行數(shù)據(jù)交換,減少了CPU介入與中斷處理,數(shù)據(jù)傳輸更流暢高效。

圖 3

RK3568J + FPGA典型應(yīng)用場景

圖 4

pcie_dma_memcpy_io_irq案例

本文主要介紹基于RK3568J + FPGA的PCIe實(shí)時(shí)通信案例,適用開發(fā)環(huán)境如下。

Windows開發(fā)環(huán)境:Windows 7 64bit、Windows 10 64bit

Linux開發(fā)環(huán)境:VMware15.5.5、Ubuntu18.04.4 64bit

U-Boot:U-Boot-2017.09

Kernel:Linux-4.19.232、Linux-RT-4.19.232

LinuxSDK:LinuxSDK-[版本號(hào)](基于rk356x_linux_release_v1.3.1_20221120)

硬件平臺(tái):創(chuàng)龍科技TL3568F-EVM工業(yè)評(píng)估板(基于瑞芯微RK3568J + 紫光同創(chuàng)Logos-2)

為了簡化描述,本文僅摘錄部分方案功能描述與測試結(jié)果,詳細(xì)產(chǎn)品資料請(qǐng)掃描文末二維碼下載。

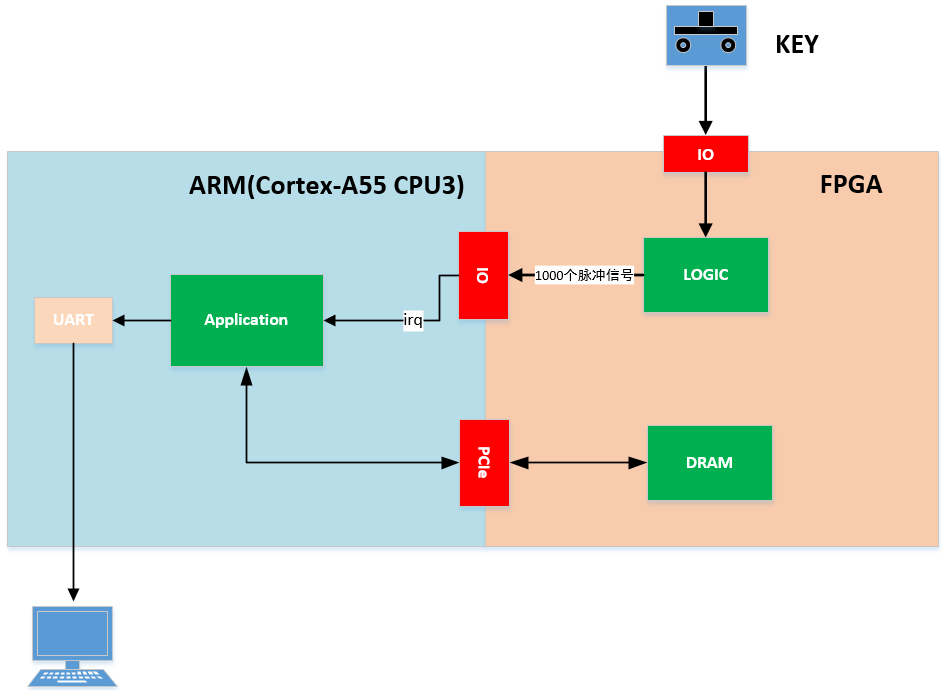

案例說明

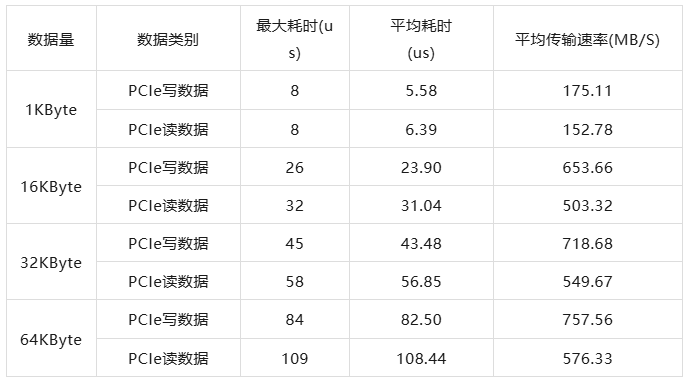

案例通過PCIe DMA在FPGA端(PCIe EP)與ARM端(PCIe RC)之間建立高速數(shù)據(jù)傳輸通道,由FPGA端按鍵觸發(fā)GPIO中斷啟動(dòng)數(shù)據(jù)傳輸,動(dòng)態(tài)調(diào)整1KByte、16KByte、32KByte、64KByte數(shù)據(jù)量并統(tǒng)計(jì)傳輸速率、延遲及誤碼率。

圖 5

案例演示

請(qǐng)參考產(chǎn)品資料完成U-Boot鏡像、內(nèi)核鏡像替換,加載FPGA可執(zhí)行程序,并將amp.img鏡像固化至評(píng)估板。

按下評(píng)估板FPGA端的USER3按鍵(KEY7),程序運(yùn)行一次。

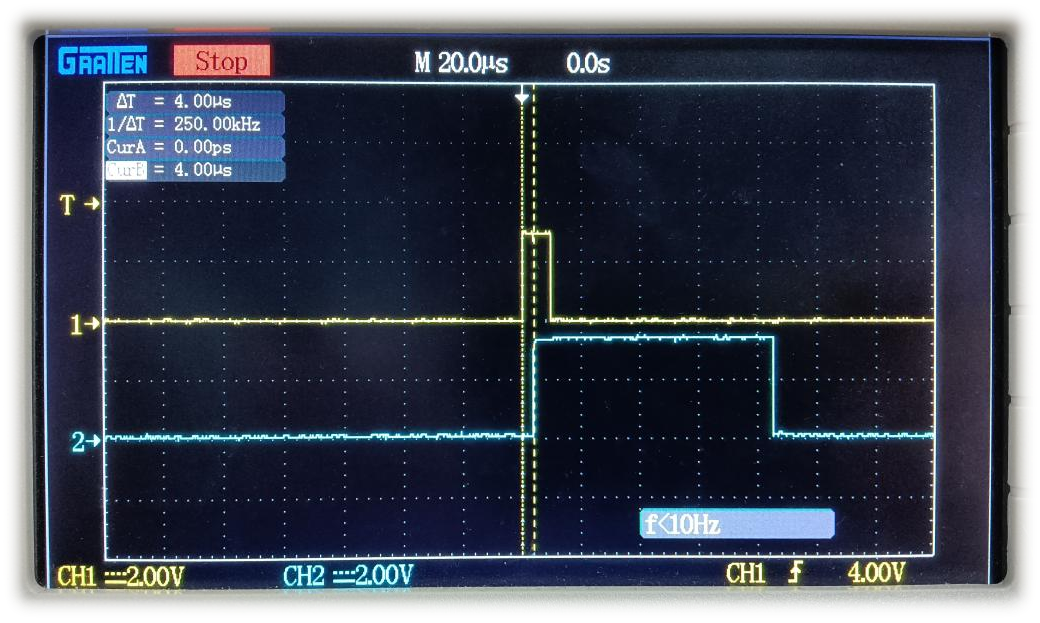

如下圖所示,使用示波器測量FPGA GPIO(黃色波形)中斷觸發(fā)至ARM GPIO(藍(lán)色波形)輸出高電平的實(shí)際耗時(shí),可看到FPGA GPIO信號(hào)上升沿至ARM GPIO信號(hào)上升沿的時(shí)間間隔約為4us,即FPGA GPIO中斷響應(yīng)時(shí)間約為4us;

圖 6

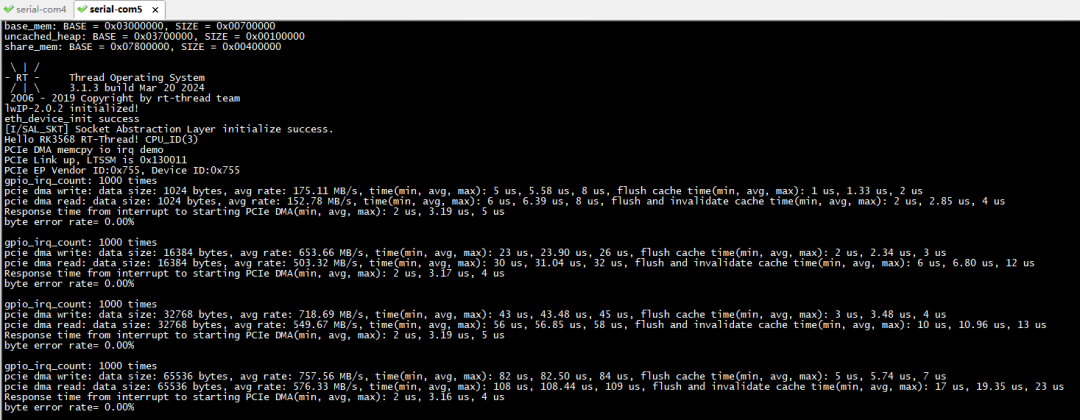

RS232 UART0串口終端將打印GPIO中斷次數(shù)、GPIO中斷響應(yīng)到啟動(dòng)PCIe DMA的耗時(shí)、PCIe平均讀寫速率、PCIe讀寫耗時(shí)、誤碼率等相關(guān)信息,如下圖所示。

從上圖RS232 UART0串口終端的打印信息可知,FPGA GPIO中斷響應(yīng)到啟動(dòng)PCIe DMA的最大耗時(shí)為4us。

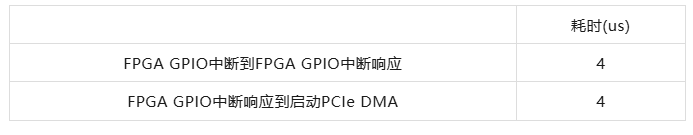

表 1 中斷響應(yīng)測試結(jié)果

表 2 PCIe讀寫速率測試結(jié)果

查看更多瑞芯微RK3568J + 紫光同創(chuàng)Logos-2相關(guān)的案例演示,各位工程師可以掃描下方二維碼下載,快來試試吧!

服務(wù)熱線

服務(wù)熱線