聯(lián)系我們

Contact Us公司總機(jī):020-8998-6280

技術(shù)熱線:020-3893-9734

技術(shù)郵箱:support@tronlong.com

銷售郵箱:sales@tronlong.com

驚艷!200MSPS采樣率,RK3588J + FPGA高速AD采集與實(shí)時顯示案例來了!

2025/01/22

測試數(shù)據(jù)匯總

測試數(shù)據(jù)匯總?cè)缦拢?/strong>

表 1

RK3588J + FPGA國產(chǎn)平臺

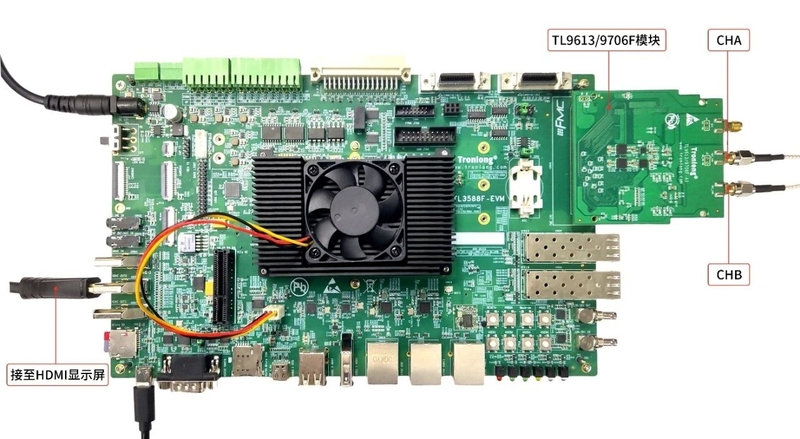

瑞芯微RK3588J/RK3588處理器集成了四核2.4GHz ARM Cortex-A76與四核1.8GHz ARM Cortex-A55。創(chuàng)龍科技基于瑞芯微RK3588J/RK3588 + 紫光同創(chuàng)Titan-2 PG2T390H(兼容Xilinx Kintex-7 XC7K325T)FPGA,推出了SOM-TL3588F工業(yè)核心板和TL3588F-EVM評估板。

RK3588J + FPGA核心板典型應(yīng)用領(lǐng)域

圖 2

pcie_ad_display案例演示

案例說明

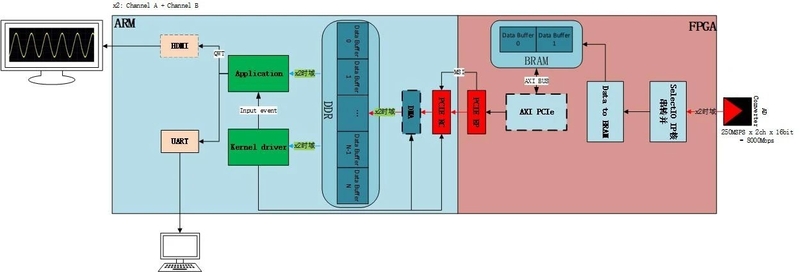

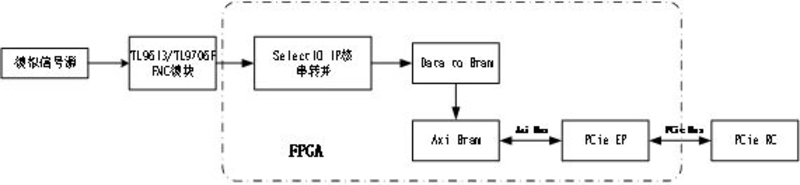

圖 2 系統(tǒng)工作示意框圖

將創(chuàng)龍科技的高速AD/DA模塊TL9613/9706F連接至評估板FMC接口,將TL9613/9706F-A1模塊的ADC_CHA和ADC_CHA通道分別正確連接至信號發(fā)生器A通道和B通道。將信號發(fā)生器設(shè)置為兩路正弦波輸出,ADC_CHA通道頻率設(shè)置為10MHz,ADC_CHB通道頻率設(shè)置為1MHz,峰峰值均設(shè)置為2.000Vpp,輸出負(fù)載均設(shè)置為50Ω。

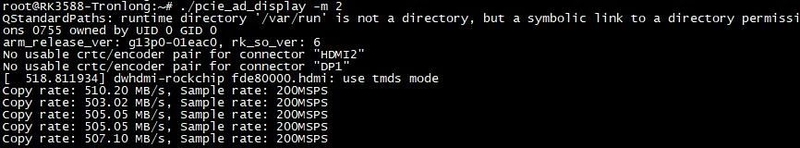

Target# ./pcie_ad_display -m 2

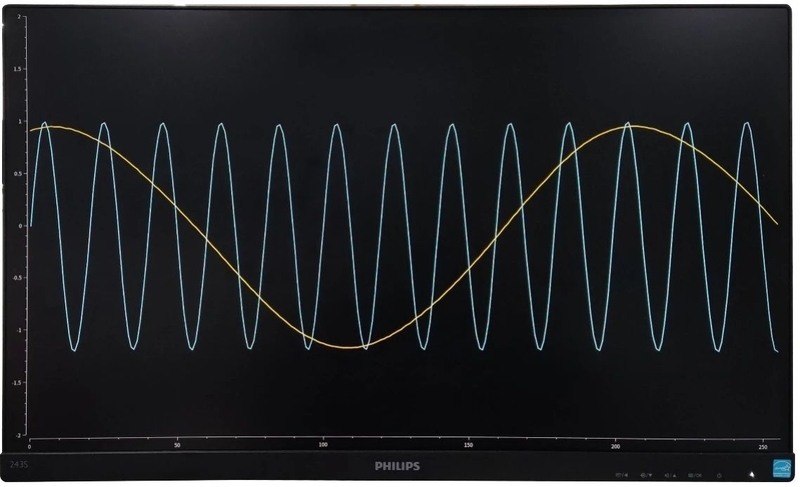

由上圖打印信息可知,讀取速率約為505MB/s,采樣率為200MSPS。同時,HDMI顯示屏將會實(shí)時顯示動態(tài)波形,如下圖所示。

至此,演示步驟就結(jié)束啦。想查看更多瑞芯微RK3588J + FPGA國產(chǎn)平臺相關(guān)案例演示,各位工程師趕緊掃描下方二維碼下載,親自體驗(yàn)一下吧!

更多FMQL20SM工業(yè)核心板產(chǎn)品資料可長按二維碼識別下載

亦可添加添加客服人員微信進(jìn)行咨詢

(即刻添加,馬上咨詢)

服務(wù)熱線

服務(wù)熱線