聯(lián)系我們

Contact Us公司總機(jī):020-8998-6280

技術(shù)熱線:020-3893-9734

技術(shù)郵箱:support@tronlong.com

銷售郵箱:sales@tronlong.com

源碼免費(fèi)下載!C6678+K7視頻采集處理方案,這里全都有!

2021/11/26

1.為什么說DSP+FPGA架構(gòu)更適合視頻采集處理?

高性能的算法處理,使用硬件描述語言去編寫算法的話,復(fù)雜程度高,工作量大,不易調(diào)試,產(chǎn)品的開發(fā)周期將非常長。這時(shí),如果為系統(tǒng)添加專為算法而生的DSP的話,將會事半功倍。

眾所周知,DSP有專門為數(shù)字信號處理所設(shè)計(jì)的指令集和流水線,可以方便高效的執(zhí)行浮點(diǎn)數(shù)和復(fù)數(shù)運(yùn)算等,這樣我們的理論算法就可以很方便的移植到實(shí)際的工程中,可以有效的縮短產(chǎn)品的開發(fā)周期。

DSP+FPGA的架構(gòu),可以把FPGA的高速采集和DSP的高性能算法處理完美結(jié)合。這種高度平衡的特性集合使其非常適合各種高性能嵌入式應(yīng)用場合,如:

■ 視頻追蹤

■ 圖像處理

■ 軟件無線電

■ 雷達(dá)探測

■ 光電探測

■ 水下探測

■ 定位導(dǎo)航

2. DSP+FPGA經(jīng)典組合——C6678+Kintex-7

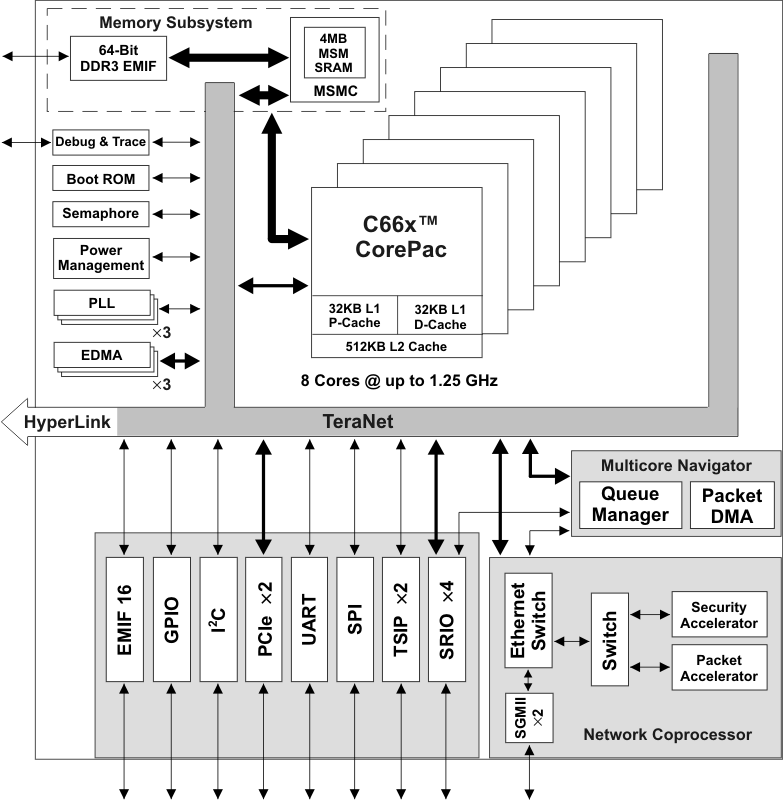

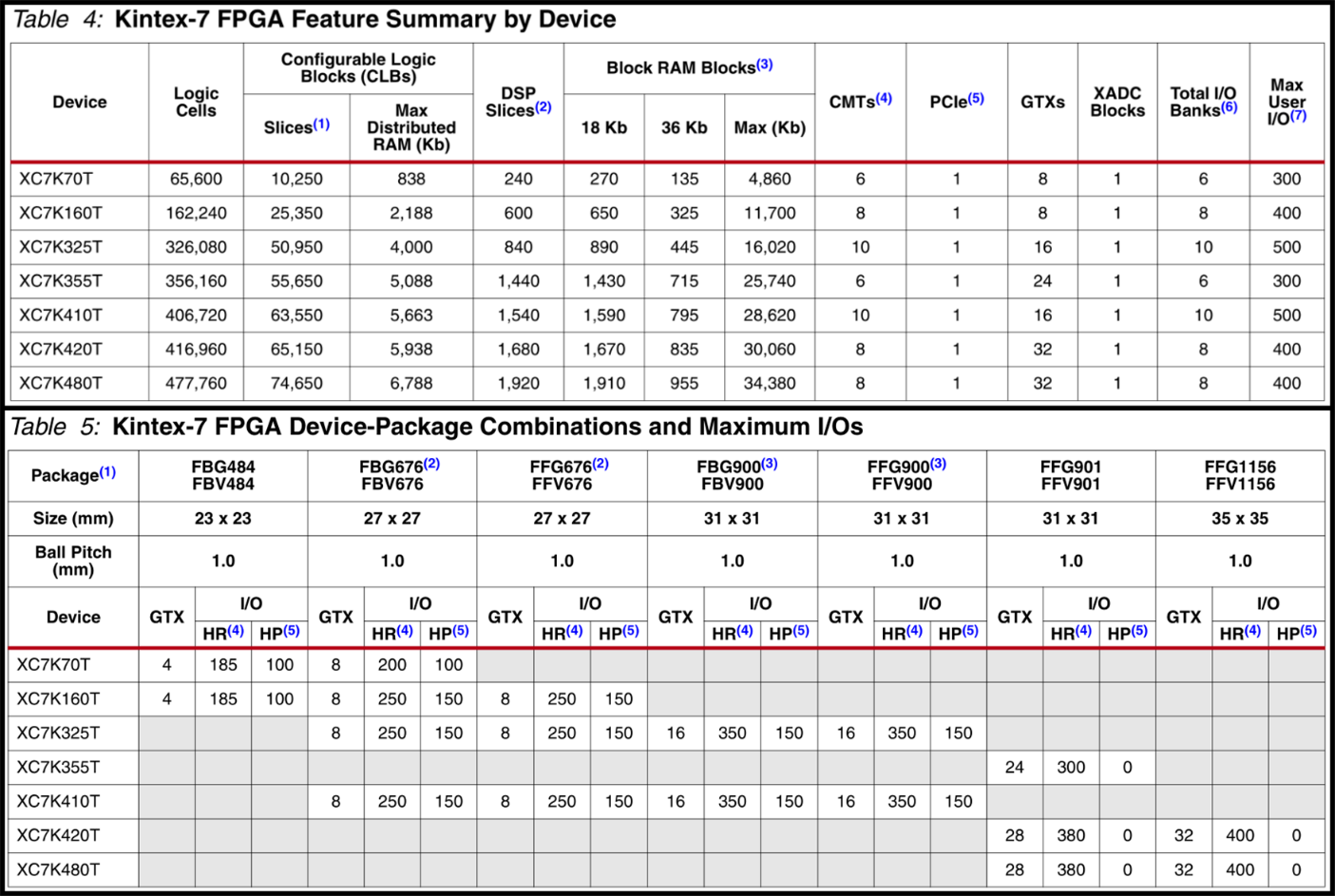

在高速圖像處理領(lǐng)域,TMS320C6678與Kintex-7進(jìn)行搭配的DSP+FPGA架構(gòu)堪稱經(jīng)典中經(jīng)典,C6678擁有8核C66x,每核主頻高達(dá)1.25GHz,同時(shí)擁有高達(dá)320 GMAC和160 GFLOP的運(yùn)算能力,可輕松駕馭圖像的復(fù)雜算法。配合Kintex-7的高速采集,完美契合各種視頻采集場景。

圖 1 TMS320C6678處理器功能框圖

圖 2 Kintex-7特性

本文基于C6678+Kintex-7平臺,為大家介紹CameraLink、SDI、PAL、HDMI的視頻采集處理綜合案例。

3. 硬件平臺

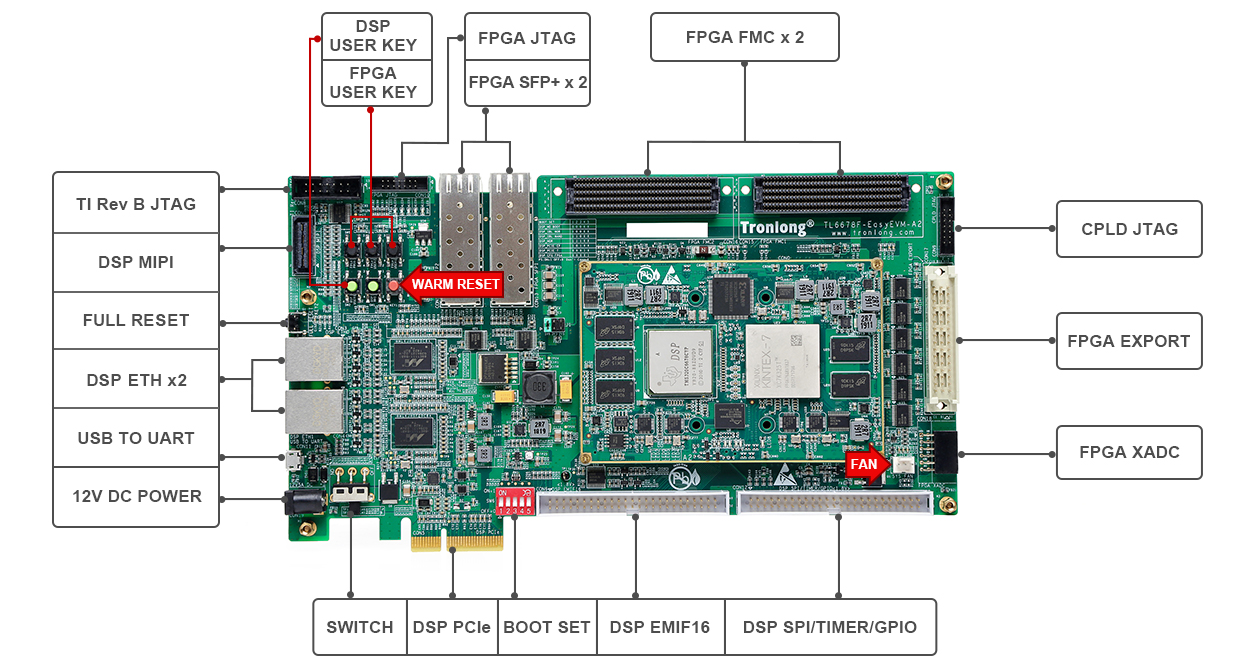

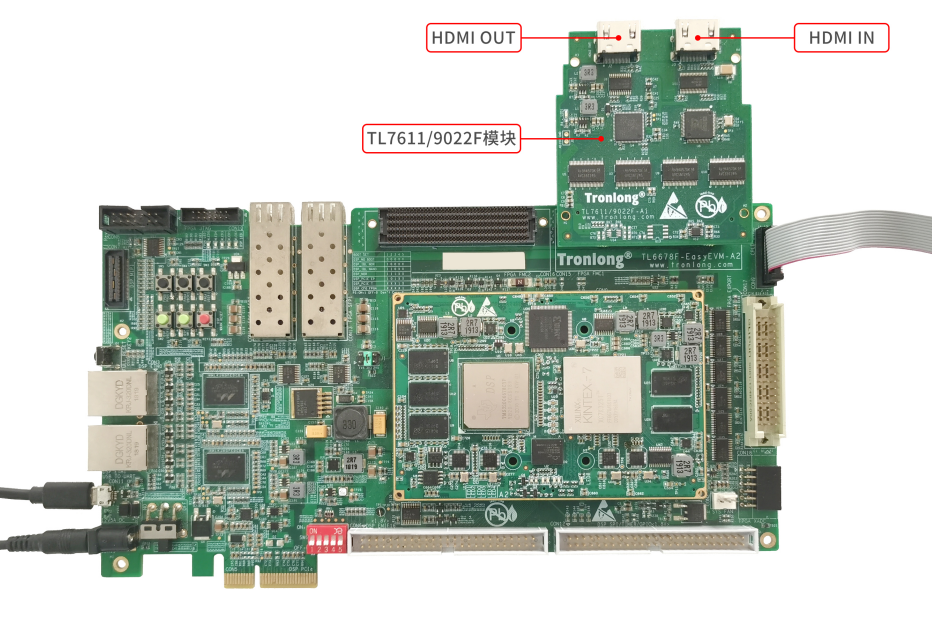

圖 3 TL6678F-EasyEVM評估板

TL6678F-EasyEVM評估板通過FMC高速接口,可接入CameraLink、SDI、PAL、HDMI等視頻采集模塊,并基于各個(gè)模塊提供了DSP+FPGA視頻采集處理綜合案例,同時(shí)提供免費(fèi)技術(shù)支持服務(wù)。

4. 視頻采集處理方案

4.1 CameraLink視頻采集處理

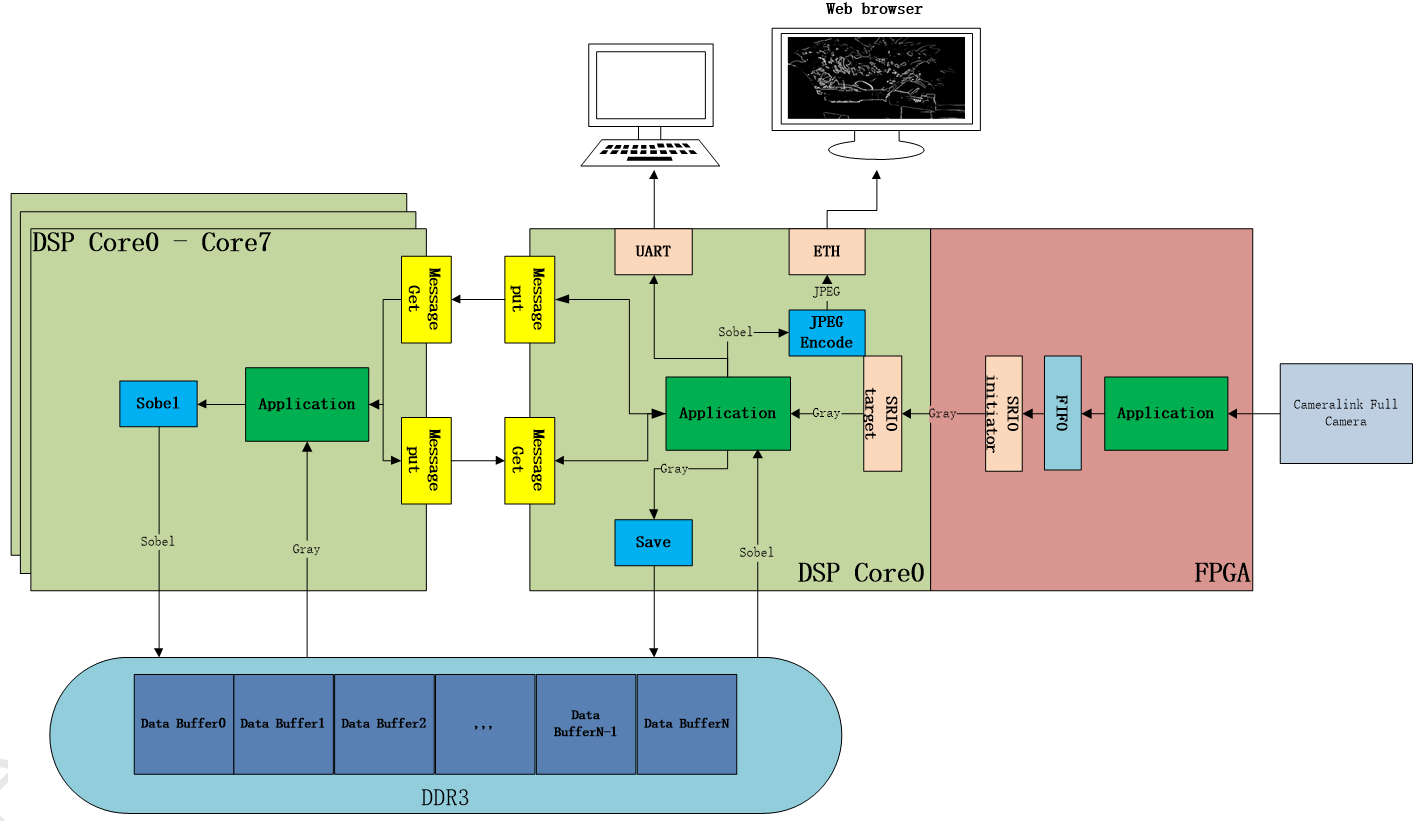

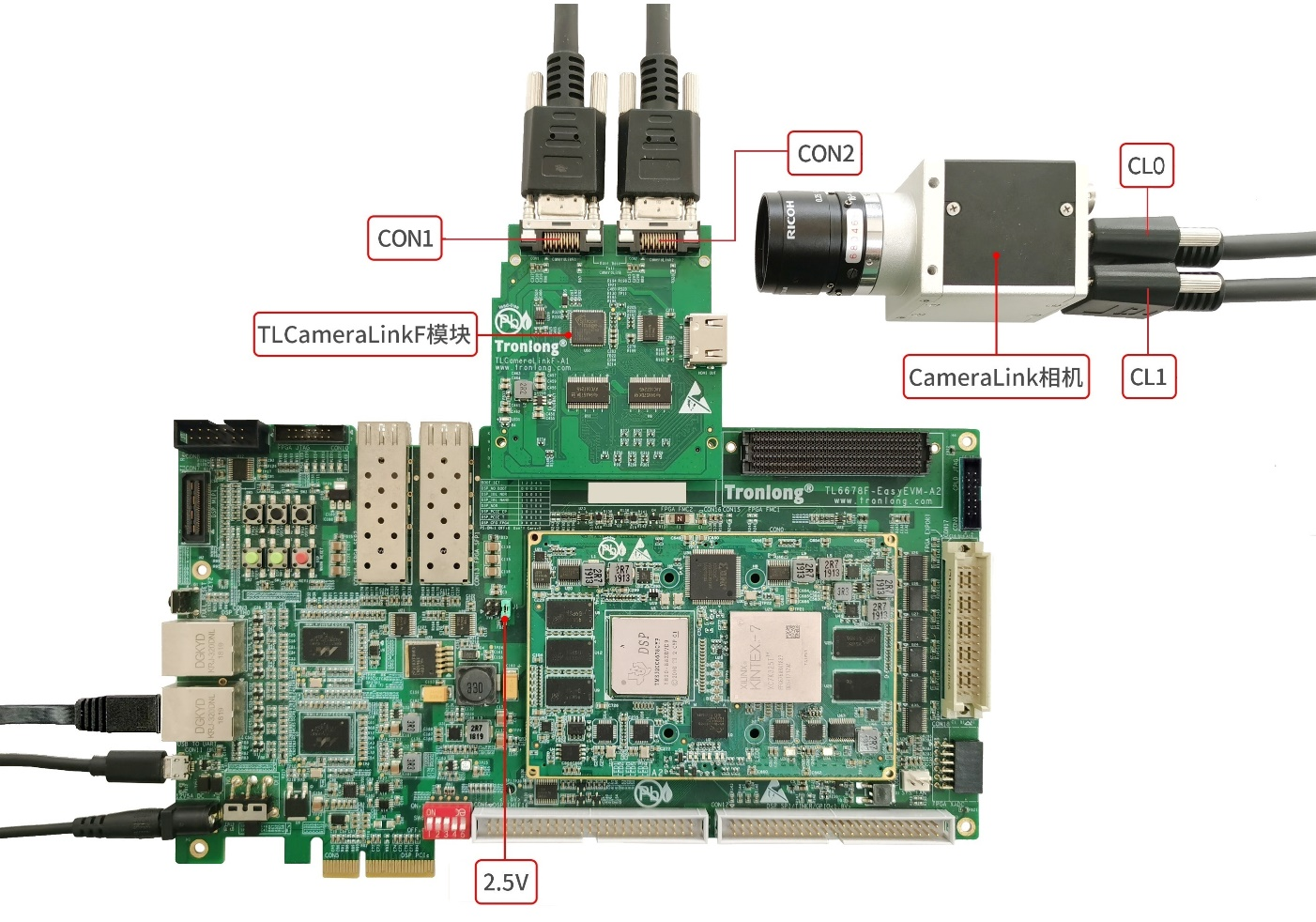

FPGA端通過FMC視頻模塊TLCameraLinkF的CameraLink接口進(jìn)行分辨率為2560 x 2048的視頻采集,再經(jīng)過SRIO總線將視頻數(shù)據(jù)傳輸至DSP端進(jìn)行Sobel(邊緣檢測)算法處理,然后將經(jīng)處理后的圖像通過網(wǎng)頁進(jìn)行顯示。

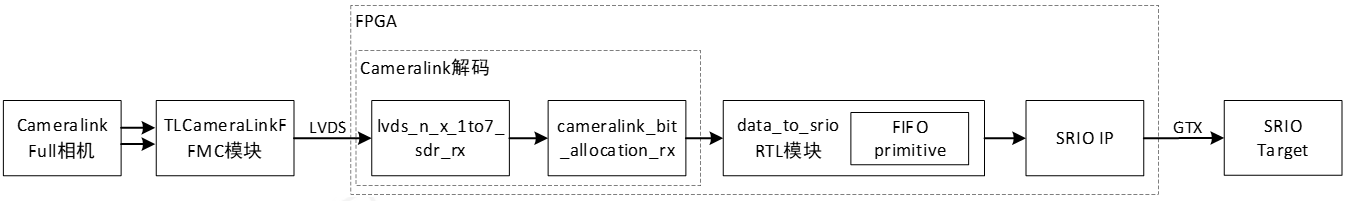

FPGA端作為SRIO Initiator,DSP端作為SRIO Target。FPGA端通過SRIO SWRITE和乒乓方式,將數(shù)據(jù)傳輸至DSP端的0x90000000和0x90500000的DDR地址空間。

案例使用北京微視的黑白CameraLink相機(jī)RS-A5241-CM107-S00,分辨率為2560 x 2048,幀率為107,灰度輸出,每個(gè)像素8bit,則數(shù)據(jù)量為2560 x 2048 x 107 x 8 = 4487905280 ≈ 4.5Gbps。案例使用SRIO的兩個(gè)Lanes,每個(gè)Lane傳輸速率為5Gbps,總數(shù)據(jù)有效帶寬為5Gbps x 2 x 80% = 8Gbps。

圖 4 案例功能框圖

圖 5 FPGA端程序功能框圖

圖 6 CameraLink模塊

圖 7 硬件連接

圖 8 測試效果圖

源碼及詳細(xì)案例說明請掃描文末二維碼進(jìn)行下載。

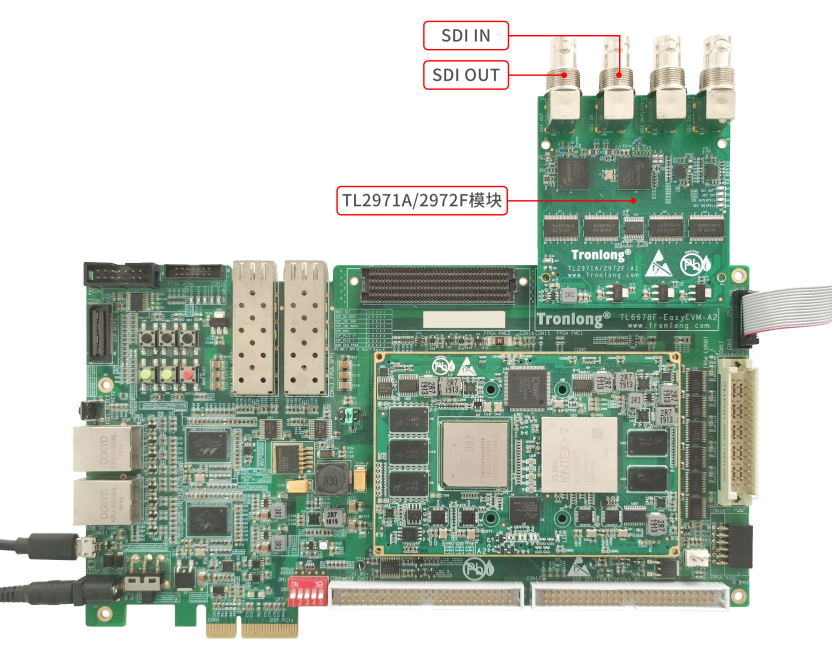

4.2 SDI視頻采集處理

Kintex-7 FPGA通過使用Video In to AXI4-Stream IP核,將SDI視頻模塊TL2971A/2972F的SDI IN接口輸入的1080P60的視頻采集進(jìn)來,并通過VDMA緩存到DDR,最后通過AXI4-Stream to Video Out IP核將視頻從模塊的SDI OUT接口輸出顯示。其中VDMA通過Microblaze配置。

圖像數(shù)據(jù)亦可通過SRIO高速總線傳輸?shù)絋MS320C6678 DSP進(jìn)行算法處理,并返回處理結(jié)果。

圖 9

圖 10 硬件連接

源碼及詳細(xì)案例說明請掃描文末二維碼進(jìn)行下載。

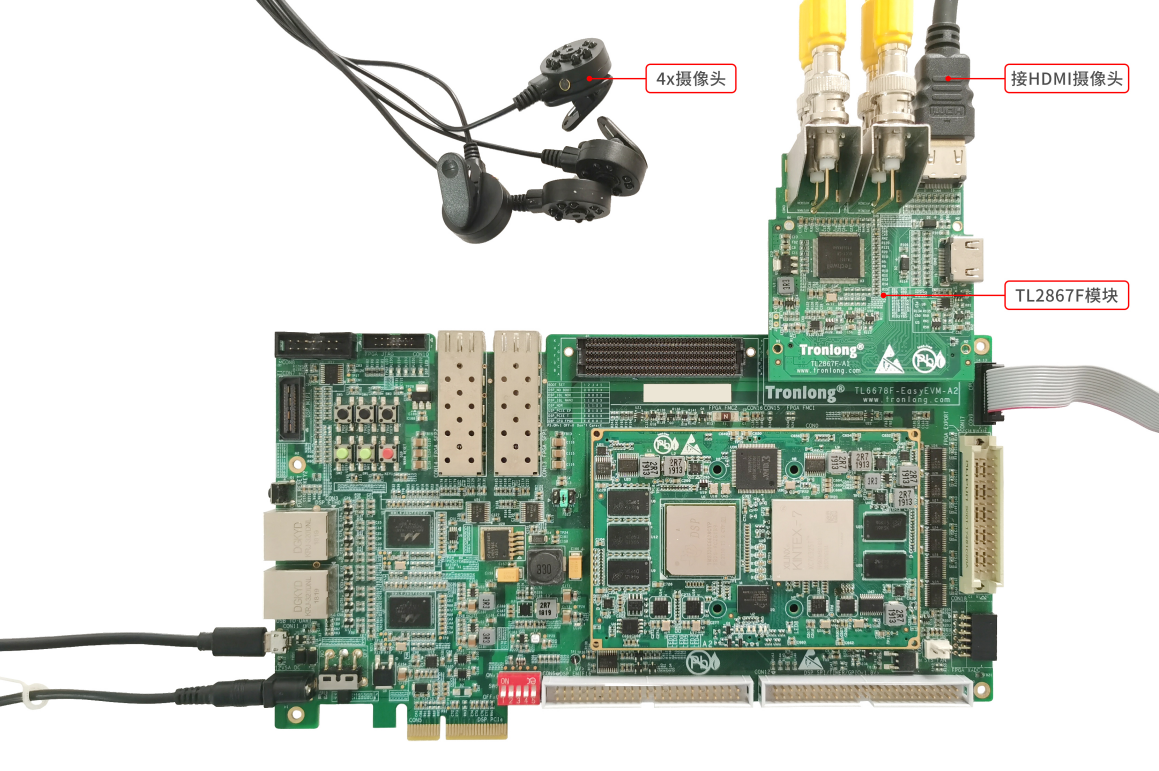

4.3 PAL視頻采集處理(4路D1)

在Kintex-7 FPGA上搭建MicroBlaze軟核,并由MicroBlaze配置PAL視頻模塊TL2867F和各IP核,將模塊輸出的一路4通道D1時(shí)分復(fù)用的復(fù)合視頻,拆分成4路獨(dú)立的BT656嵌入式同步視頻,再將4路視頻進(jìn)行BT656解碼分離出同步信號和像素?cái)?shù)據(jù)。使用VDMA IP緩存到內(nèi)存設(shè)備上,通過VPSS IP將4路圖像進(jìn)行去交錯(cuò),然后由Mixer IP將四路圖像拼接起來,通過rgb2dvi邏輯模塊,將RGB視頻信號轉(zhuǎn)換為DVI視頻信號,最后通過模塊的HDMI1接口輸出顯示到顯示器。支持PAL制式(分辨率為720x576)視頻輸入,輸出顯示分辨率為1280x1024。

圖像數(shù)據(jù)亦可通過SRIO高速總線傳輸?shù)絋MS320C6678 DSP進(jìn)行算法處理,并返回處理結(jié)果。

圖 11

圖 12

圖 13 硬件連接

圖 14

源碼及詳細(xì)案例說明請掃描文末二維碼進(jìn)行下載。

4.4 HDMI視頻采集處理

Kintex-7 FPGA使用Video In to AXI4-Stream IP核,通過HDMI視頻采集模塊TL7611/9022F的HDMI IN接口將1080P60視頻采集進(jìn)來,并通過VDMA緩存到DDR,最后通過AXI4-Stream to Video Out IP核將視頻從模塊的HDMI OUT接口輸出顯示。其中VDMA IP核,HDMI OUT芯片(SIL9022)和HDMI IN芯片(ADV7611)通過MicroBlaze運(yùn)行裸機(jī)程序進(jìn)行配置。

圖像數(shù)據(jù)亦可通過SRIO高速總線傳輸?shù)絋MS320C6678 DSP進(jìn)行算法處理,并返回處理結(jié)果。

圖 15

圖 16 硬件連接

源碼及詳細(xì)案例說明請掃描文末二維碼進(jìn)行下載。

5 源碼、資料下載

案例源碼、產(chǎn)品資料(用戶手冊、核心板硬件資料、產(chǎn)品規(guī)格書)可點(diǎn)擊該超鏈接

6. 技術(shù)交流群

TMS320C6678 DSP交流群:79635273、332643352

Kintex-7 FPGA交流群:311416997、101245165

服務(wù)熱線

服務(wù)熱線