聯(lián)系我們

Contact Us公司總機:020-8998-6280

技術(shù)熱線:020-3893-9734

技術(shù)郵箱:support@tronlong.com

銷售郵箱:sales@tronlong.com

【稀缺資源】基于FPGA的CameraLink OUT視頻案例

2021/04/16

上周創(chuàng)龍科技(Tronlong)發(fā)布了TL6678ZH-EVM(C6678+Zynq-7045/7100)評估板的V1.1版本的資料更新,重點內(nèi)容就是CameraLink OUT視頻案例,具體清單如下:

(1)更新DSP端網(wǎng)絡(luò)相關(guān)案例Demo源碼;

(2)新增《DSP RTOS綜合功能案例測試手冊》,包含DSP端IFD案例;

(3)更新《ZYNQ PS+PL異構(gòu)多核案例開發(fā)手冊》,新增axi_10g_ethernet_dma案例(AXI(10G)光口通信,新增udp_10g_dma案例(UDP(10G)光口通信),新增aurora_dma案例PL端MicroBlaze工程;

(4)更新《ZYNQ PL端案例開發(fā)手冊》,新增udp_10g_echo案例;

(5)更新《ZYNQ視頻案例開發(fā)手冊》,新增cameralink_display和cameralink_loopback案例(CameraLink視頻輸出);

(6)更新《DSP+ZYNQ通信案例開發(fā)手冊》,新增SRIO_AD9613綜合案例(基于SRIO的高速AD(AD9613)采集處理),新增SRIO_CameraLink綜合案例(基于SRIO的CameraLink視頻采集處理),新增flash_dsp案例(通過ZYNQ固化DSP程序至SPI FLASH)。

圖 1 TL6678ZH-EVM評估板資源框圖

圖 2 TL6678ZH-EVM評估板資源框圖

CameraLink視頻輸出在行業(yè)應(yīng)用中,最主要的作用是為下級處理系統(tǒng)提供高幀率視頻源,幀率可高達幾百幀。其實大家可以發(fā)現(xiàn),市面上關(guān)于CameraLink視頻輸入案例的較多,但公開的CameraLink視頻輸出案例極少,這在較大程度上阻礙了客戶新產(chǎn)品研發(fā)進度。

創(chuàng)龍科技收集眾多客戶關(guān)于CameraLink的需求后,為解決客戶的視頻開發(fā)痛點,加快客戶產(chǎn)品開發(fā)速度,故推出本篇CameraLink OUT案例,下面就一起來看下案例的詳細介紹吧!

如需獲取CameraLink OUT案例源碼、TL6678ZH-EVM評估板或其他產(chǎn)品詳細資料,請即刻掃描下方二維碼或點擊下載鏈接。

http://site.tronlong.com/pfdownload

1案例功能

演示平臺:TL6678ZH-EVM(C6678+Zynq-7045/7100)評估板

案例功能:本案例作用是驗證CameraLink接口在Base模式下的視頻輸出功能。評估板通過HDMI IN接口進行720P60的視頻采集,并通過CameraLink2接口將采集到的視頻進行輸出,再通過CameraLink1接口接入來自CameraLink2接口的視頻輸出信號,最后通過HDMI OUT接口進行視頻輸出。

圖 3

2操作說明

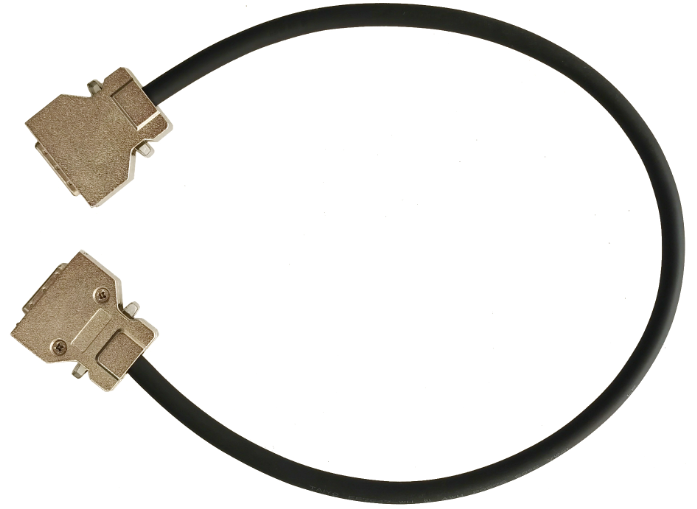

準(zhǔn)備一臺擁有HDMI OUT接口的PC機(例如筆記本),通過HMDI數(shù)據(jù)線將PC機HDMI OUT接口連接至評估板的HDMI IN接口,PC機HDMI OUT接口用作圖像輸出。通過HMDI數(shù)據(jù)線將一臺HDMI顯示屏連接至評估板的HDMI OUT接口,HDMI顯示屏用作圖像顯示。使用創(chuàng)龍科技的CameraLink回環(huán)線(型號:MDR-MDR 0.5m)連接評估板的CameraLink1、CameraLink2接口。

圖 4

圖 5 CameraLink回環(huán)線

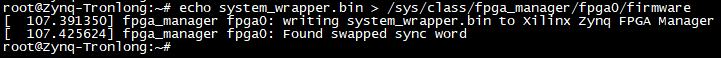

將本案例的PL端.bin格式可執(zhí)行文件復(fù)制到"/lib/firmware/"目錄下,并將PL端可執(zhí)行文件重命名為system_wrapper.bin,然后執(zhí)行如下命令加載PL端可執(zhí)行文件。

Target# echo system_wrapper.bin > /sys/class/fpga_manager/fpga0/firmware

圖 6

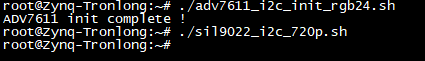

將案例"sw\linux_system\image\"目錄下所有腳本文件拷貝至評估板文件系統(tǒng),并執(zhí)行如下命令。

Target# ./adv7611_i2c_init_rgb24.sh

Target# ./sil9022_i2c_720p.sh

圖 7

在PC機的顯卡設(shè)置(或圖形屬性)中,按照下圖設(shè)置HDMI分辨率為1280 x 720、刷新率為60pHz,即可看到HDMI顯示屏輸出PC機輸出的原始圖像。

圖 8

圖 9

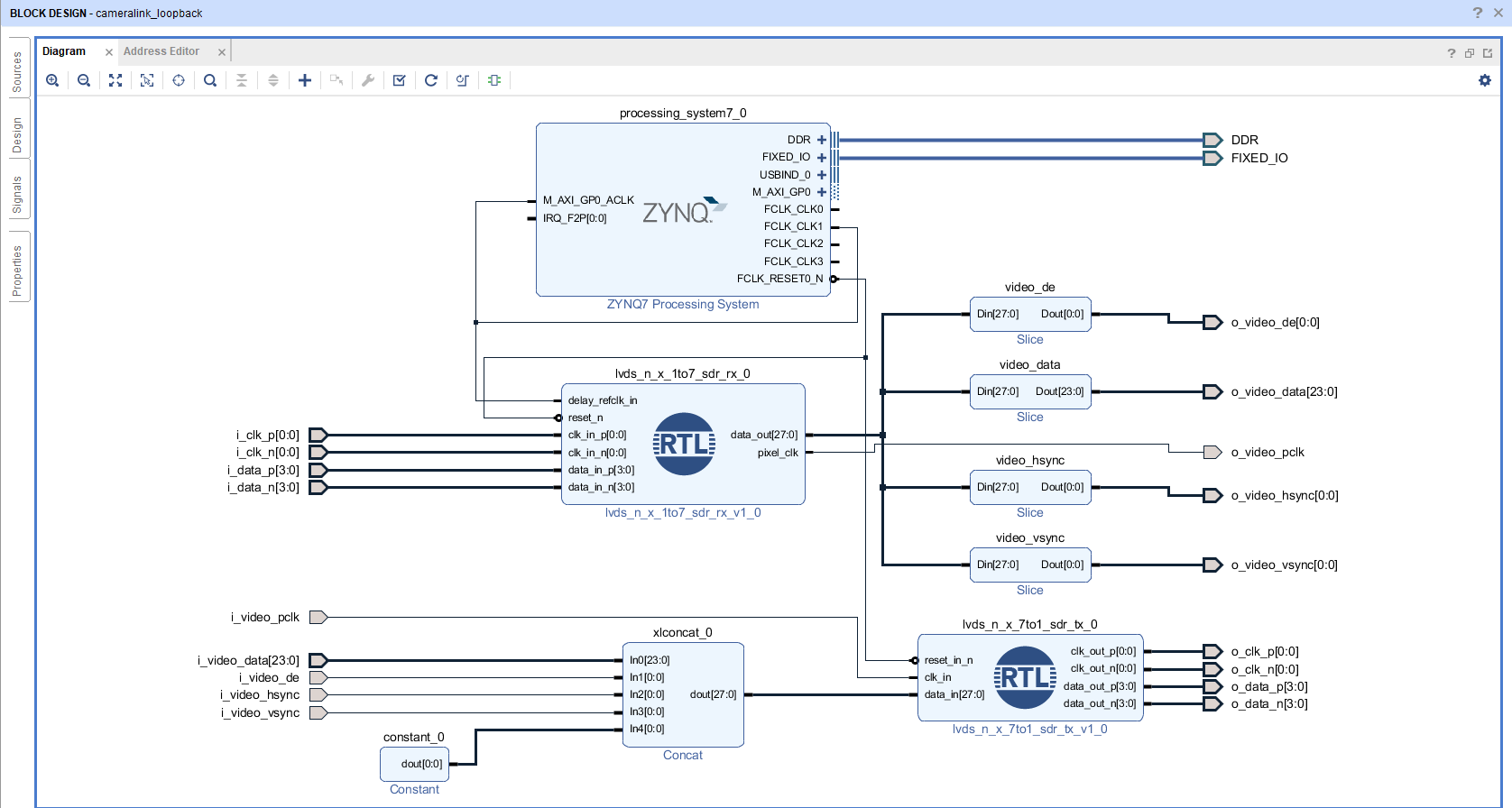

3Vivado工程說明

打開BLOCK DESIGN開發(fā)界面,可查看Vivado工程。

圖 10

4模塊配置

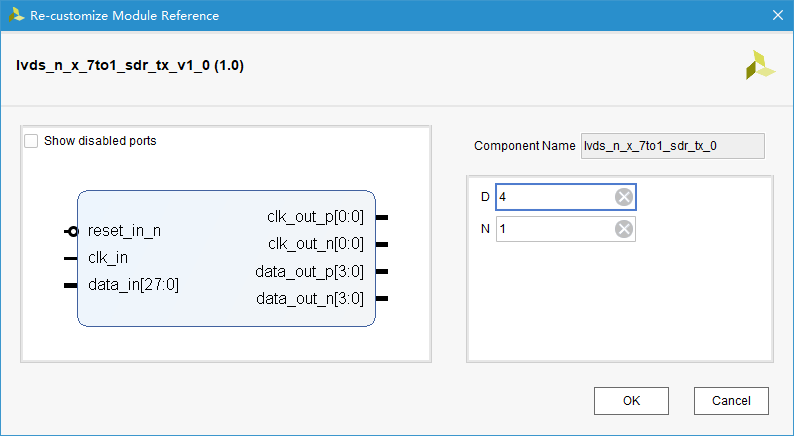

4.1lvds_n_x_7to1_sdr_tx模塊

本案例使用lvds_n_x_7to1_sdr_tx模塊將HDMI IN接口輸入的并行數(shù)據(jù)轉(zhuǎn)化成差分數(shù)據(jù),LVDS使用SDR模式,在時鐘的單邊沿傳輸數(shù)據(jù)。

lvds_n_x_7to1_sdr_tx模塊開發(fā)文檔為產(chǎn)品資料“6-開發(fā)參考資料\Xilinx官方參考文檔\”目錄下的《xapp585-lvds-source-synch-serdes-clock-multiplication.pdf》。lvds_n_x_7to1_sdr_tx模塊源碼文件為Vivado工程"cameralink_loopback.srcs\sources_1\imports\hdl\lvds_n_x_7to1_sdr_tx.v",具體配置說明如下。

(1)配置N(通道數(shù)量)為3對應(yīng)Full模式,配置N為1則對應(yīng)Base模式。配置D為4,表示“每個通道的數(shù)據(jù)差分對數(shù)量為4”。

?Base模式:單通道,每通道數(shù)據(jù)差分對為4組,需1個連接器。

?Medium模式:雙通道,每通道數(shù)據(jù)差分對為4組,需2個連接器。

?Full模式:三通道,每通道數(shù)據(jù)差分對為4組,需2個連接器。

圖 11

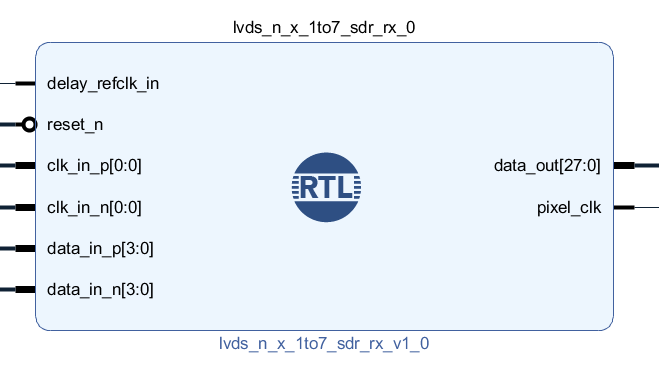

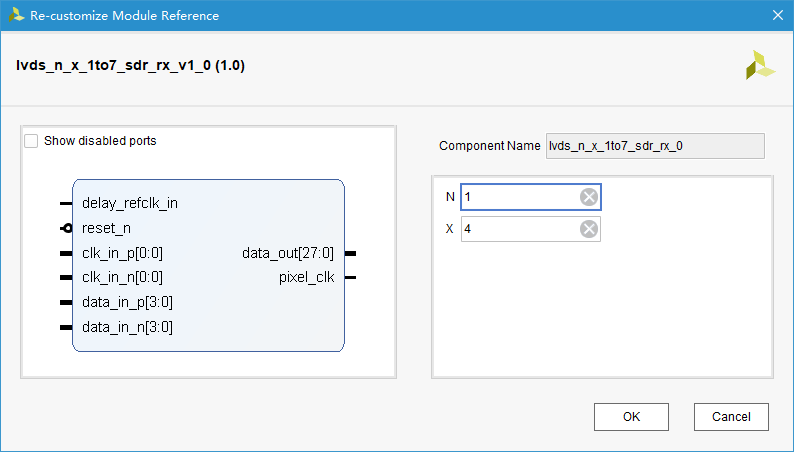

4.2lvds_n_x_1to7_sdr_rx模塊

本案例使用lvds_n_x_1to7_sdr_rx模塊將CameraLink1接口輸入的差分視頻數(shù)據(jù)轉(zhuǎn)化成并行視頻數(shù)據(jù)。

lvds_n_x_1to7_sdr_rx模塊開發(fā)文檔為產(chǎn)品資料“6-開發(fā)參考資料\Xilinx官方參考文檔\”目錄下的《xapp585-lvds-source-synch-serdes-clock-multiplication.pdf》。lvds_n_x_1to7_sdr_rx模塊源碼文件為Vivado工程"cameralink_loopback.srcs\sources_1\imports\hdl\lvds_n_x_1to7_sdr_rx.v",具體配置說明如下。

(1)delay_refclk_in接入由PS端輸出的200MHz參考時鐘。

圖 12

(1)配置N(通道數(shù)量)為3對應(yīng)Full模式,配置N為1則對應(yīng)Base模式。配置X為4,表示“每個通道的數(shù)據(jù)差分對數(shù)量為4”。

?Base模式:單通道,每通道數(shù)據(jù)差分對為4組,需1個連接器。

?Medium模式:雙通道,每通道數(shù)據(jù)差分對為4組,需2個連接器。

?Full模式:三通道,每通道數(shù)據(jù)差分對為4組,需2個連接器。

圖 13

服務(wù)熱線

服務(wù)熱線